١

## BD 955 BROADCAST DIGITAL AUDIO DELAY LINE

# INSTRUCTION MANUAL

EVENTIDE INC. • ONE ALSAN WAY • LITTLE FERRY, NEW JERSEY 07643 • 201-641-1200 • TWX: 710-991-8715

### LIMITED WARRANTY

## ALL EVENTIDE EQUIPMENT IS WARRANTED FOR A PERIOD OF ONE YEAR

from the date of purchase from Eventide or an authorised dealer, against defects in material or workmanship. In case of difficulty, consult Eventide or your dealer for instructions.

This warranty does not apply to mechanical defects caused by use or rough handling, or to damage caused by improper operation not in accordance with this manual. Cause of defect is in the sole judgement of Eventide. There are no other express or implied warranties, and no warranty of merchantability or fitness for a particular purpose.

The warranty is voidable at Eventide's option under the following circumstances:

- if the equipment is connected to an improper voltage supply.

- if the user makes unauthorized modifications of any type. If such modifications are made, user agrees to pay for any time or parts necessary to remove the modification before repair.

Eventide will under no circumstances be responsible for consequential damages caused by failure of equipments of its manufacture, or for any other reason. Our sole liability is for repair or replacement of defective parts, under the terms of the warranty.

#### SHIPPING

Equipment should be returned, if possible, in the original packing container. Loose cards must be wrapped in conductive foil (damage caused by failure to do this will render the warranty void). If the original container is not available, the equipment must be packed to prevent damage from crushing or dropping. Damage caused by inadequate packing for service return is not covered by warranty. We recommend shipping via UPS rather than by US mail, and air freight if you are in a hurry. If in our opinion the packing container is inadequate for return shipment, we reserve the right to supply a new container and charge for same.

The warranty covers return shipping in the continental US except Alaska. Return shipments will not be insured unless the customer requests and agrees to pay for same. If a more expensive form of shipment is requested, customer will be charged for same.

ALL RETURNED UNITS, IN OR OUT OF WARRANTY, MUST BE PREPAID TO OUR DOOR.

ALL RETURNED UNITS MUST BE ACCOMPANIED BY A COMPLETE TROUBLE REPORT, DETAILING ALL THE PROBLEMS EXPERIENCED, CONDITIONS OF OPERATION, ETC.

#### FOREIGN SHIPMENTS

Foreign shipments must be returned fully prepaid, including Customs and brokerage charges. Repaired equipment will be shipped all charges collect. A commercial invoice stating 'goods of US manufacture - being returned for repair' and giving a fair market value of the unit should accompany the shipment, to save time and expense. A copy of this invoice should also be mailed to Eventide.

REPLACEMENT OF PARTS UNDER WARRANTY will be done free of charge provided that the defective parts and the warranty card for the unit are received by Eventide.

3/79

T/

....

WARRANTY REGISTRATION FORM MODEL BD955 DIGITAL DELAY LINE

γĹ

ہے۔ ا

.....

| SERIAL NUMBERDELAY 6.4SEC () 3.2SEC () 1.6SEC (                                                      |

|------------------------------------------------------------------------------------------------------|

| BANDWIDTH 7.5kHz () 15kHz () STEREO MASTER () SLAVE ()                                               |

| DATE PURCHASED                                                                                       |

| YOUR COMPANY                                                                                         |

| ADDRESS                                                                                              |

| CITY/STATE/ZIP                                                                                       |

| STATION CALL LETTERS AM ( ) FM ( )                                                                   |

| STATION CALL LETTERS AM ( ) FM ( )                                                                   |

| CHIEF ENGINEER'S NAME                                                                                |

| Person to whom data should be sent if TITLE different from Chief Engineer                            |

| Site where equipment will be located if different from above                                         |

| •                                                                                                    |

| Is this site the studio? ( ) transmitter ( ) both ( )                                                |

| From whom did you purchase this delay line? FACTORY? () DISTRIBUTOR/REP? (                           |

| If distributor, please give name and location                                                        |

| How did you learn about this product?                                                                |

| Additional space for comments if desired. Thank you.                                                 |

|                                                                                                      |

| * * * *                                                                                              |

| Please check if you would like information on other Eventide products:                               |

| H969 Harmonizer <sup>®</sup> ( ) . H949 Harmonizer <sup>®</sup> ( ) H910 Harmonizer <sup>®</sup> ( ) |

| SP2016 Signal Processor ( ) JJ193 Delay Line ( ) 2830 Omnipressor <sup>®</sup> ( )                   |

| RETURN FORM TO:                                                                                      |

EVENTIDE INC. • ONE ALSAN WAY • LITTLE FERRY, NEW JERSEY 07643 • 201-641-1200 •

Π

Ľ

ĺ

亡~亡

الم ال

Ļ

| Warranty<br>Warranty Form                                    | i<br>ii       |

|--------------------------------------------------------------|---------------|

| Introduction                                                 | 2             |

| Specifications                                               | 4             |

| Front Panel Controls                                         | 5 8           |

| Front Panel Indicators                                       | 8             |

| Input Level Setting                                          | 9             |

| Rear Panel Connectors                                        | 10            |

| System Interconnection                                       | 11            |

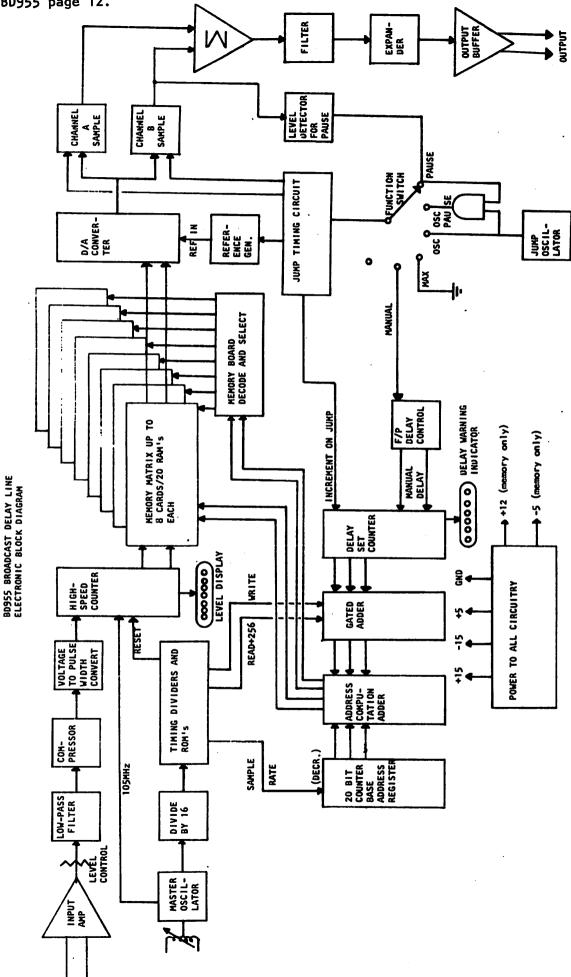

| Electronic Block Diagram                                     | 12            |

| THEORY OF OPERATION:                                         |               |

| Timing Oscillator                                            | 13            |

| Timing Chain                                                 | 13            |

| Analog/Digital Converter                                     | 14            |

| Input Signal Conditioning                                    | 14            |

| Catch-Up Mode                                                | 16            |

| Controlling the JUMP Command                                 | 16            |

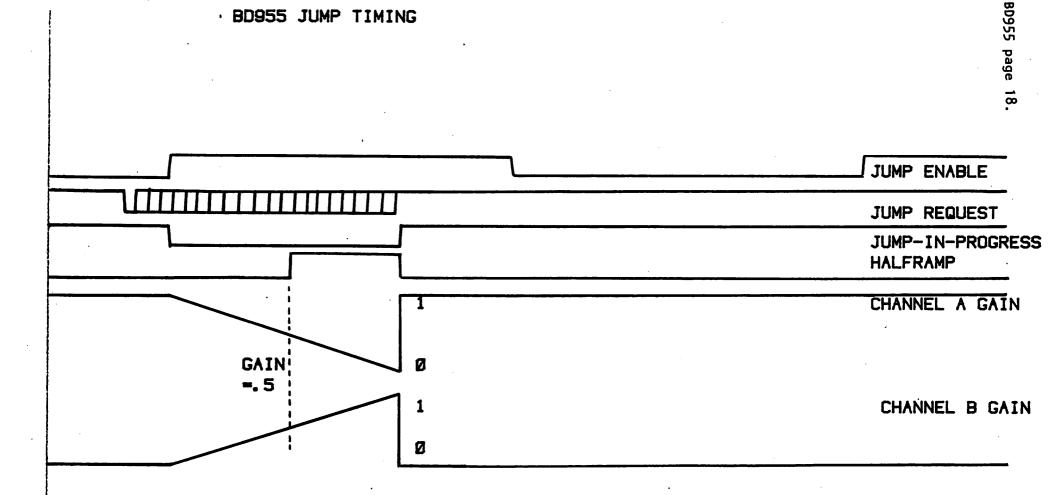

| JUMP Timing Diagram                                          | 18            |

| Writing Data to the Memory                                   | 19            |

| Stereo Interconnection                                       | 22            |

|                                                              |               |

| INTERNAL ADJUSTMENTS AND ALIGNMENT PROCEDURE:                |               |

| Pause Level Control                                          | 23            |

| Oscillator Frequency                                         | 23            |

| Input Gain                                                   | 23            |

| Output Gain                                                  | 23            |

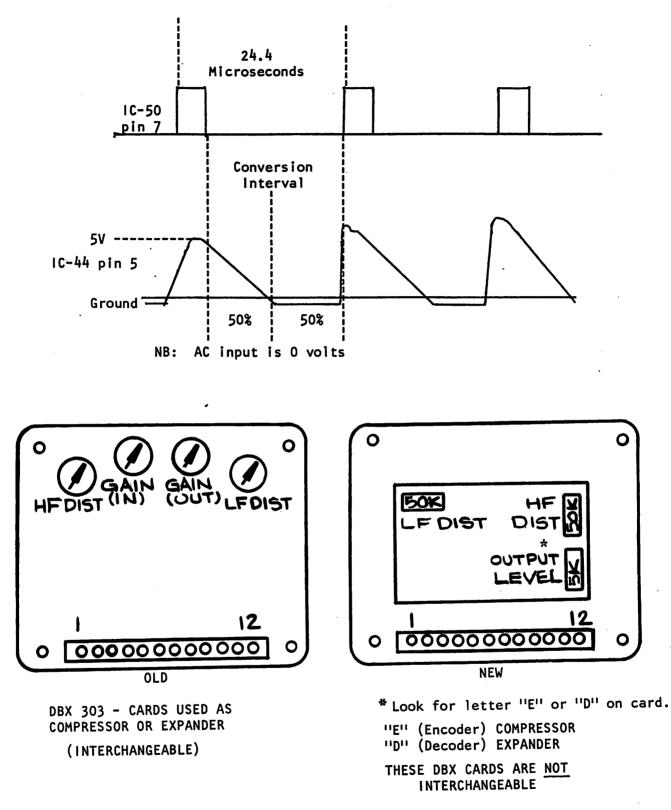

| A/D Converter Waveforms (diagram)                            | 24            |

| Compander Card Top View (diagram)                            | 24            |

| Oscillator Frequency Adjustment                              | 25            |

| Analog/Digital Converter Current Sink Adjustment             | 25            |

| Input and Output Companders                                  | 25            |

| Pause Level Control                                          | 25            |

| A/B Offset Control Adjustment                                | 26            |

| "Full Gate" Input DIP Switch                                 | 26            |

| DUMP Lamp Jumper                                             | 26            |

| A/B Offset Pot Adjustment (diagram)                          | 27            |

| DIP Switch (diagram)                                         | 27            |

|                                                              |               |

| TROUBLESHOOTING (emergency and otherwise):                   | 28            |

| Timing Chain                                                 | 28            |

| Companders                                                   | 20            |

| Main Timing Diagram                                          | 30<br>31      |

| Lengthening the Maximum Delay                                | 31            |

| SCHEMATICS:                                                  |               |

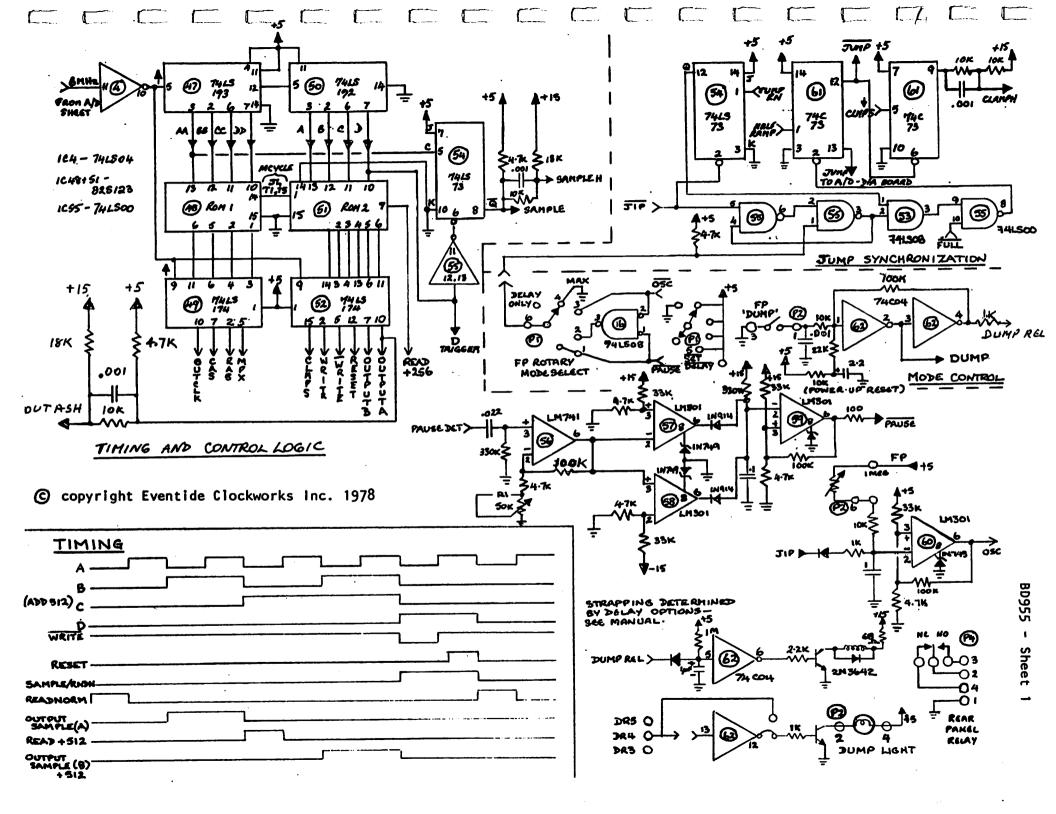

| Timing and Control Logic                                     | Sheet 1       |

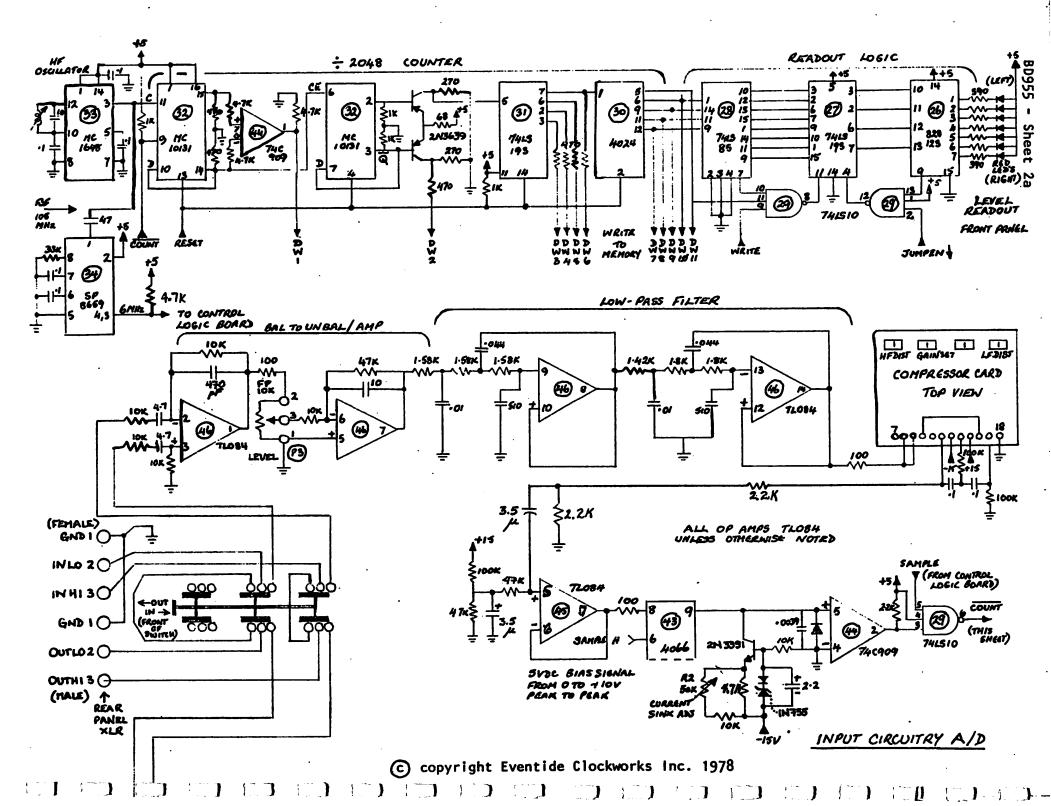

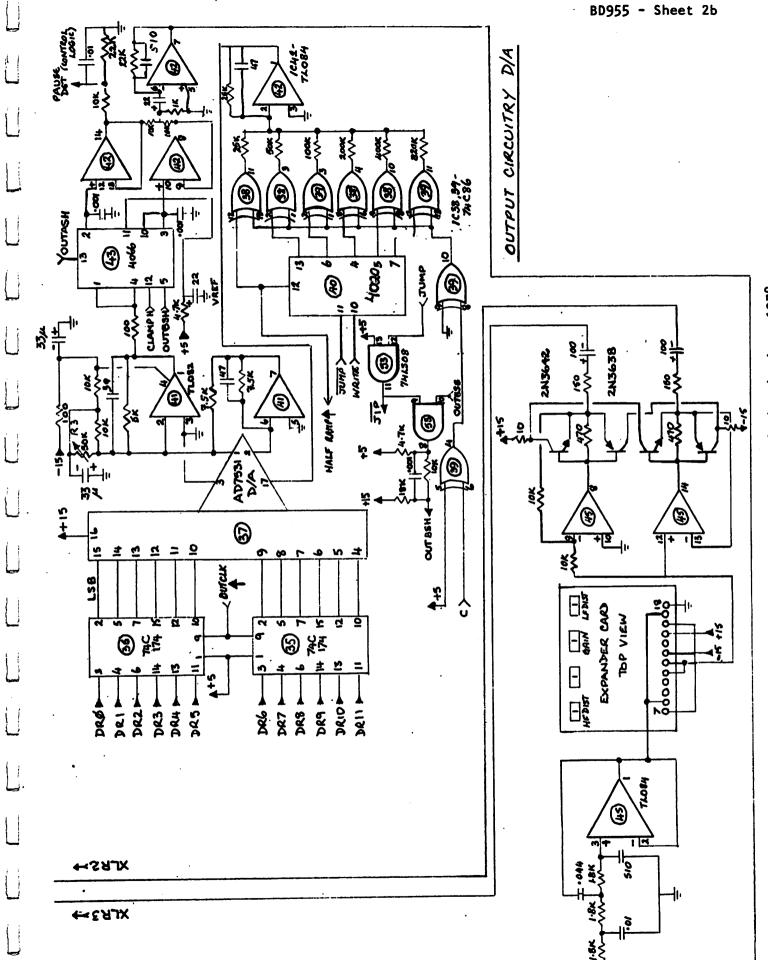

| Input Analog A/D, Output D/A                                 | Sheet 2a & 2b |

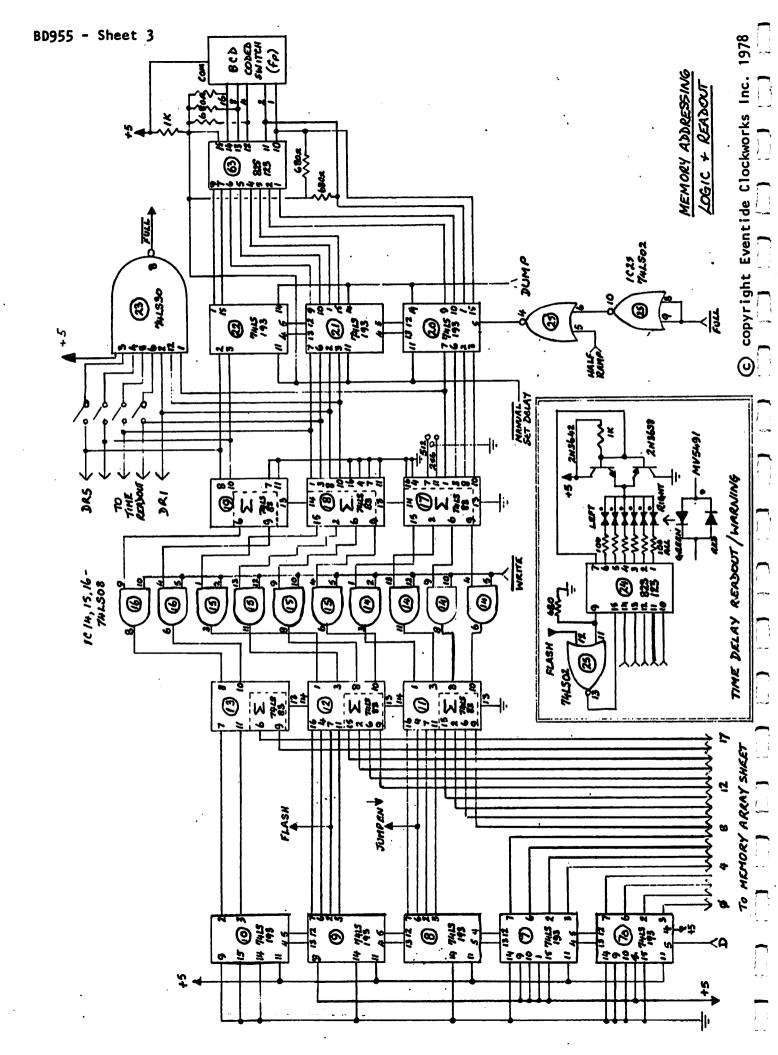

| Memory Addressing Logic and Readout                          | Sheet 3       |

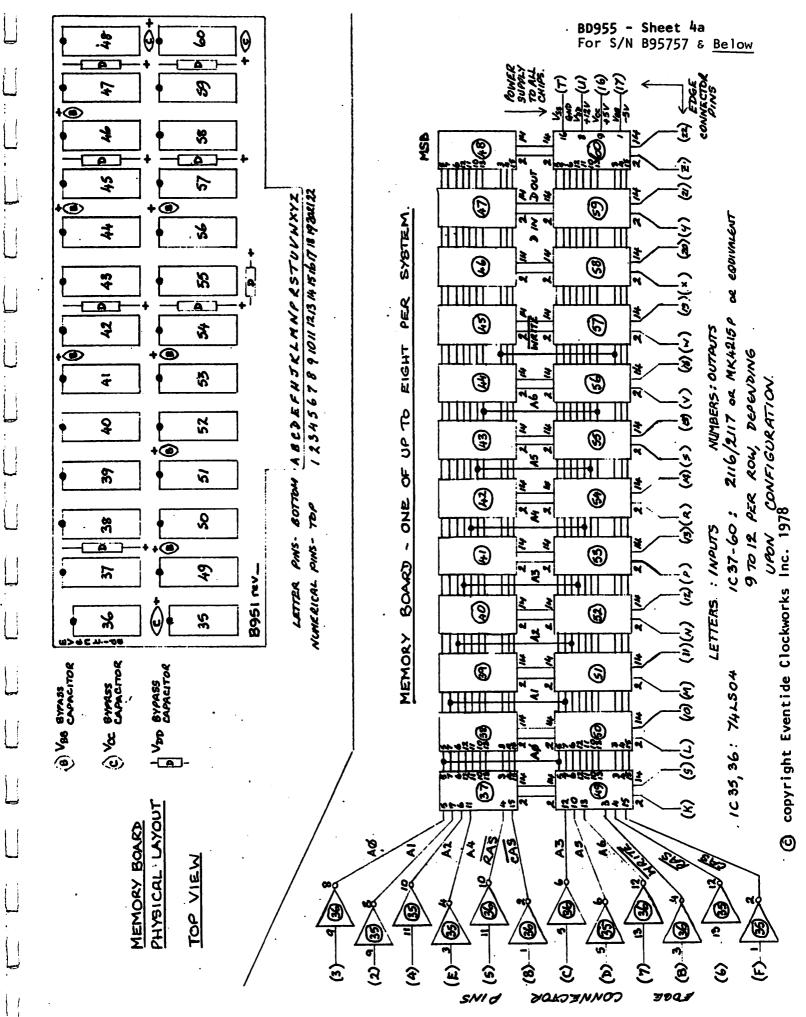

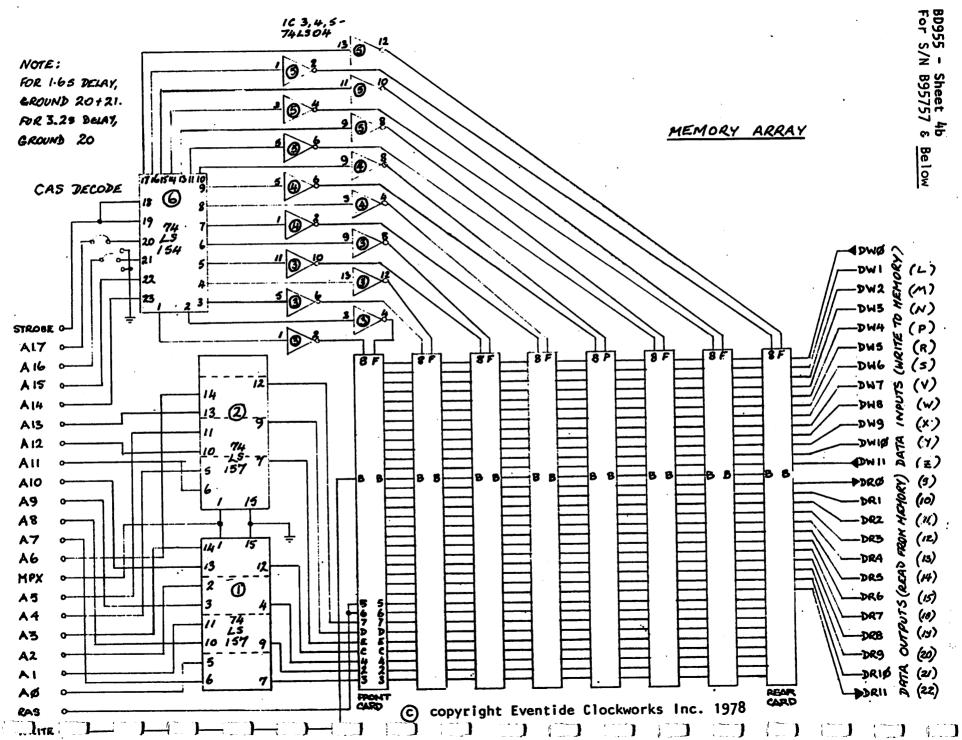

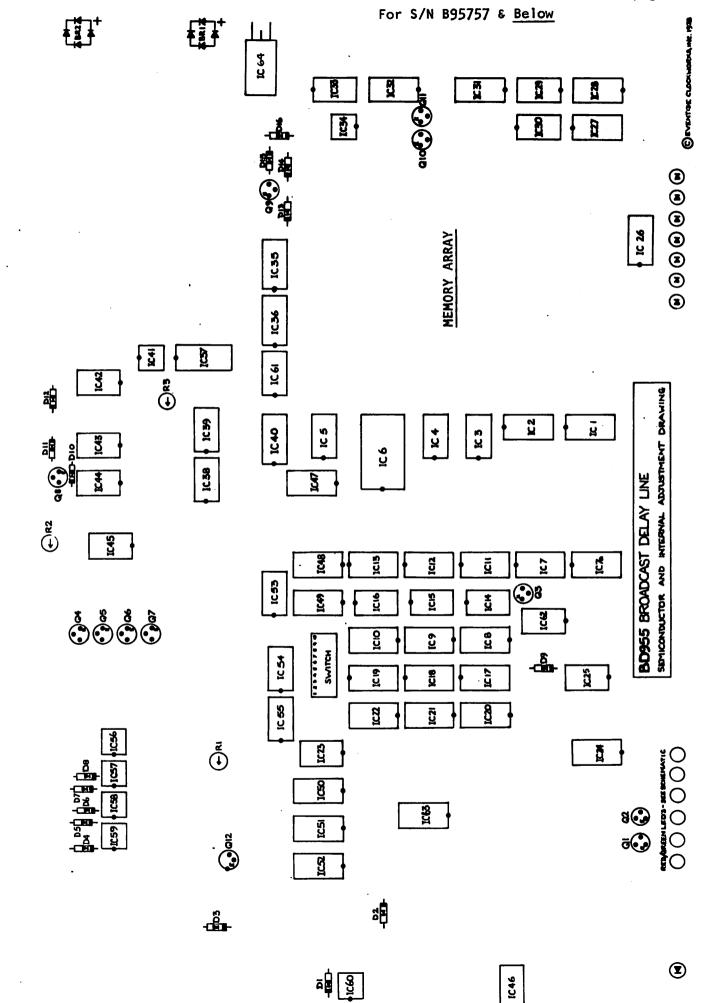

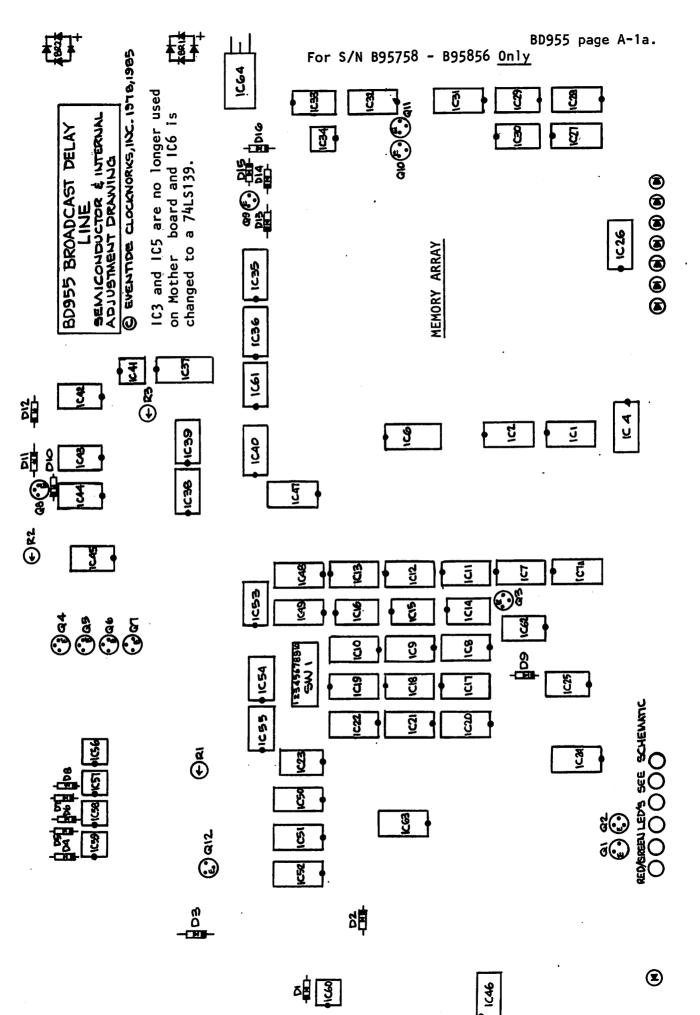

| Memory Board and Array for BD955's with S/N B95757 & Below   | Sheet 4a & 4b |

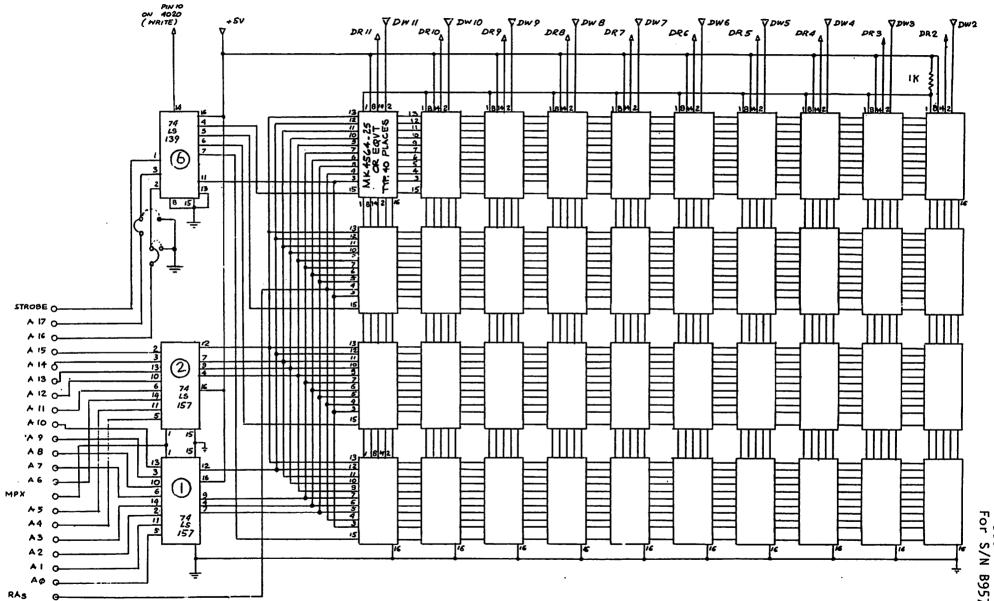

| Memory Board for BD955's with S/N B95758 & Above             | Sheet 4c      |

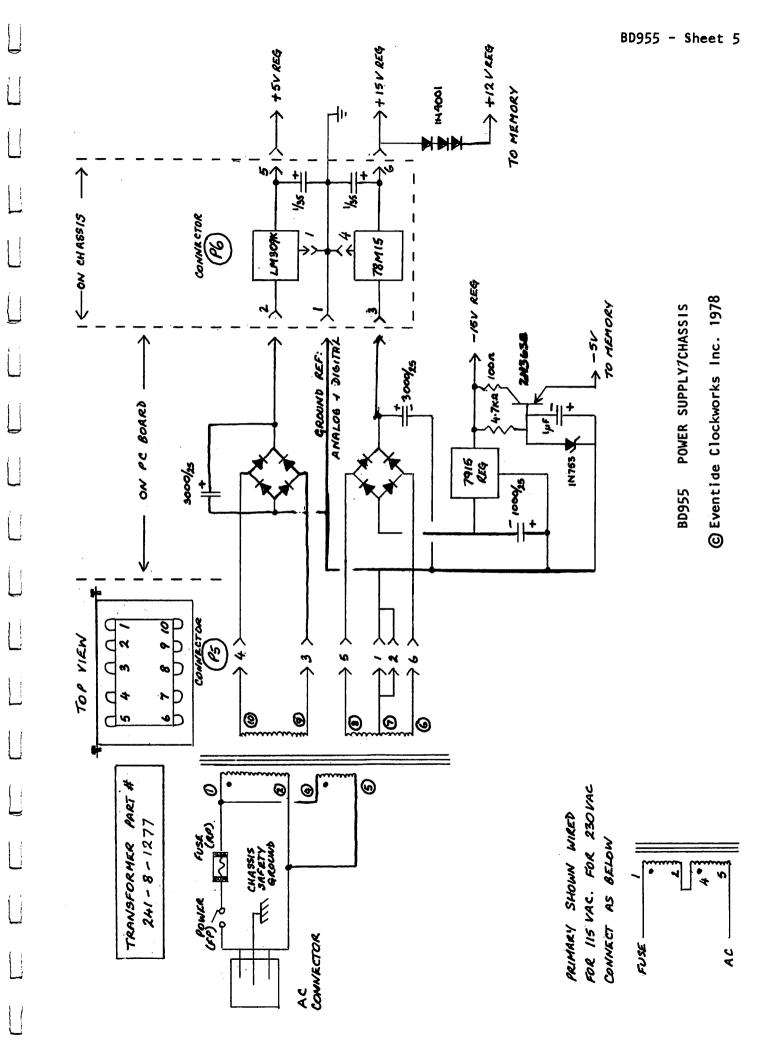

| Power Supply and Chassis                                     | Sheet 5       |

|                                                              | Sheet 6       |

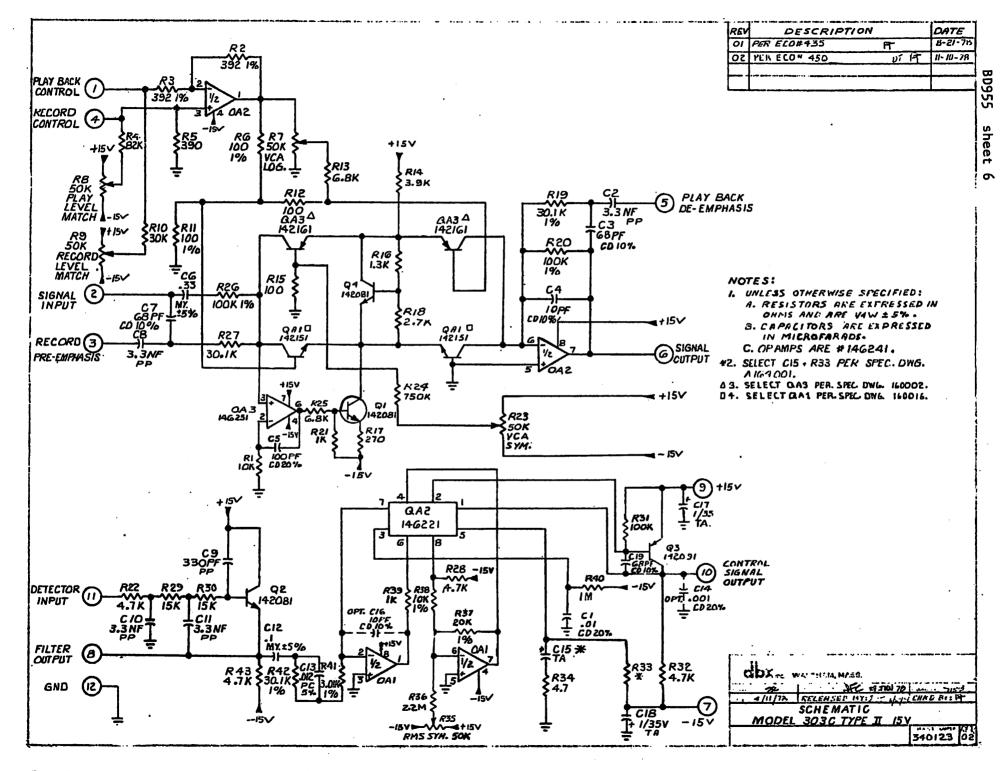

| Compander Card                                               |               |

| APPENDIX:                                                    |               |

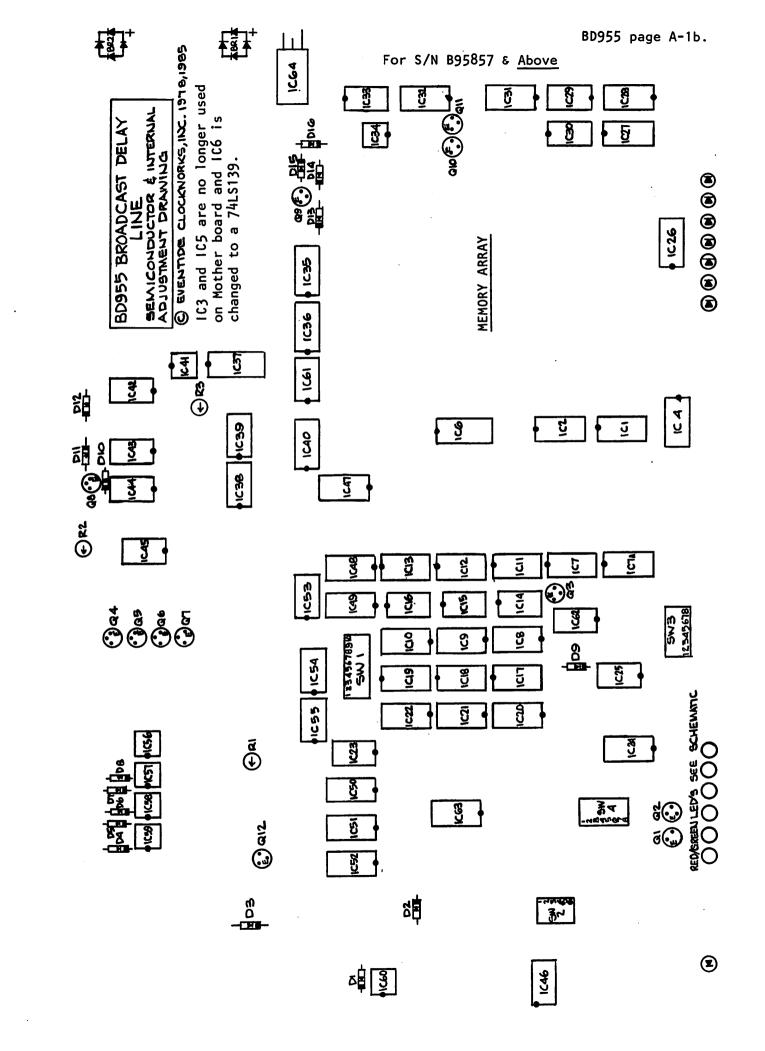

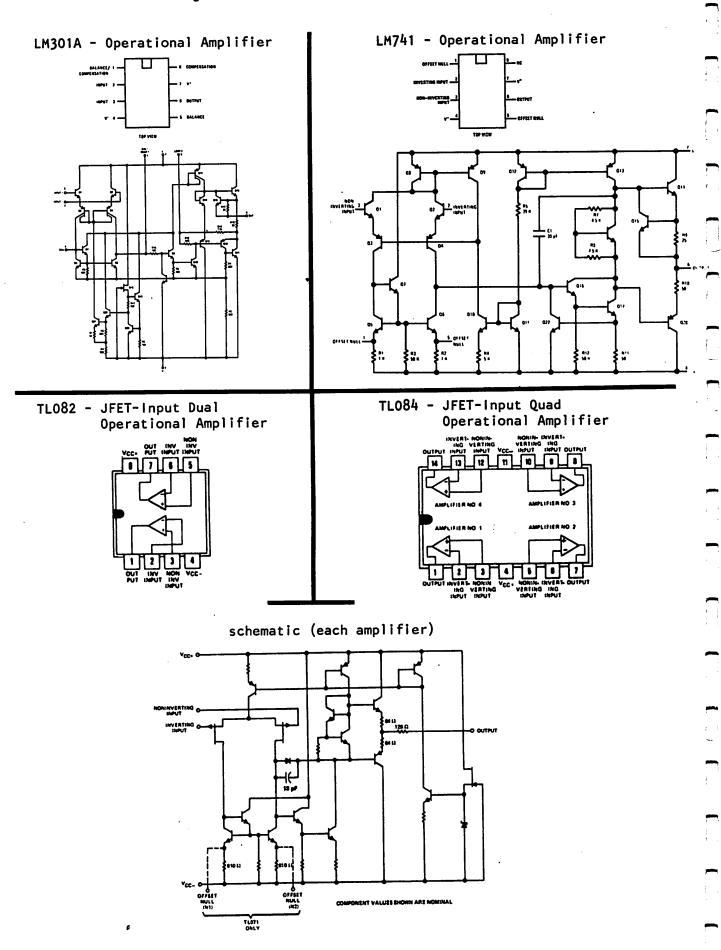

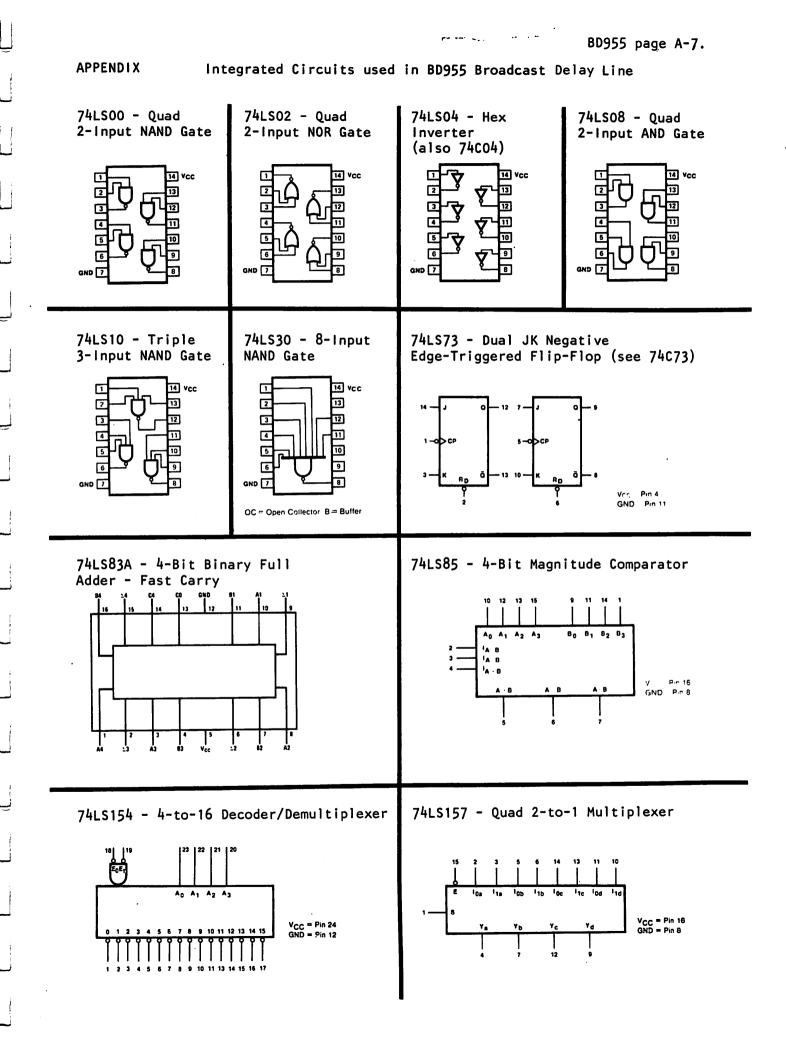

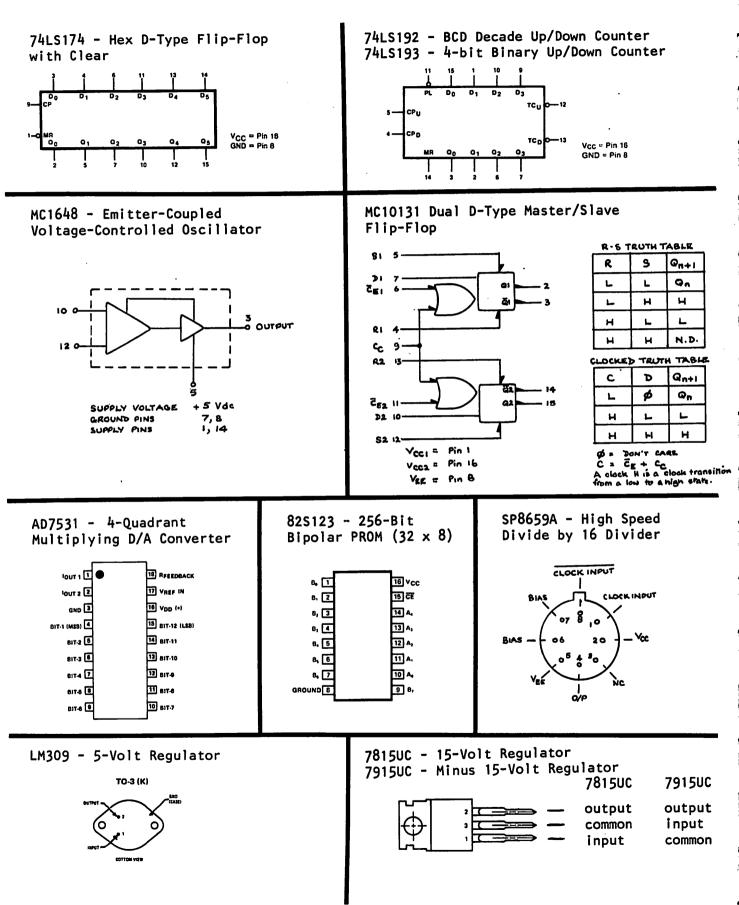

| Semiconductor and Internal Adjustment Drawing                | A-1           |

| <ul> <li>Diodes and Transistors used in the BD955</li> </ul> | A-2           |

| Integrated Circuits used in the BD955, with Pinout Diagrams  | s A-3         |

| -                                                            |               |

#### INTRODUCTION

The BD955 Broadcast Digital Delay Line is designed to enable the broadcast licensee to meet his obligation to the public and to the regulatory authorities to prevent obscene and/or libelous material from being transmitted over his facilities. It does this by automatically delaying program material by up to 6.4 seconds, thus allowing time for the monitoring operator to make the decision as to whether the material being delayed fits in either category.

If it does, either of two methods may be used to ensure that material is not aired. The first of these methods is standard: A taped jingle, censor's beep, or announcement is placed on the air and the delay line output is temporarily cut off. The second method is unique: newly developed electronic circuitry (patent pending) allows the entire contents of the delay to be "dumped", and the program resumed without interruption. Auxiliary circuitry can be used if desired to prevent uncontrolled sources (such as telephone callers) from being aired until the delay is again long enough to provide protection.

Additional features of the delay line include the ability to generate short delays for use in audio production applications, and to synchronize audio and video in cases where video is transmitted via satellite and audio via landline.

When compared to the traditional method of delay using tape loops, cartridges, or even two recorders with the tape stretched between them, the BD955 exhibits greater reliability, better and more consistent quality, no requirement for operator attention, and, in cases where it is used continually, lower monetary cost compared to that of a high quality tape machine that would be otherwise unavailable. Of course, the unique variable delay capabilities used in the "catch up" mode are mechanically unobtainable, as are the short delay times so useful in production and synchronization applications.

This instruction manual covers use, principles of operation, technical data, and contains alignment and troubleshooting data should this be required. We have also reprinted a copy of the "blurb sheet" for your convenience. May we take this opportunity to thank you for purchasing this Eventide unit, and to encourage you to return the warranty sheet. This will permit us to furnish corrections and updates, as well as possible application notes and future product announcements. If you have any questions or comments we should be pleased to hear from you.

### THE DIGITAL BROADCAST DELAY LINE THAT BREAKS MURPHY'S LAW! No tape loops that snap. No moving parts that break. No dead air.

The Eventide BD955 broadcast digital audio delay line offers memory capacity to delay signals up to 6.4 seconds. It also incorporates a unique "catch-up" feature, which eliminates the need for a taped jingle or announcement.

#### **EXCLUSIVE CATCH-UP MODE**

With the BD955, it's easy to get in and out of delay operation. After pressing the DUMP button, an exclusive mode of operation allows the program to continue in real time, without the necessity for filling the delay period with a jingle or announcement. Instead, as the DUMP button is depressed, the delay goes to zero, and the obscenity is deleted. Then, the delay increases at a variable rate while the program is continuing, so that a new delay margin for deletion is built up. This catch-up mode does not introduce wow, and is virtually undetectable in operation. A front panel display shows, in digital form (a progression of lighting LED's), how much margin the announcer has. Until the delay is fully restored, he will have to be more alert, but the mode permits much faster resumption of the program, without false interruptions. The catch-up mode may be defeated if normal delay operation is required.

#### A VALUABLE PRODUCTION TOOL

When not being used as an editing delay, the BD955 delay line may be used as a production tool. Front panel switches allow setting the delay from about 6.5 milliseconds to the unit's maximum delay, a range useful for many production effects, including so-called 'doubling', or giving the audible illusion of multiple speakers, singers or instrumentalists.

**BROADCAST DIGITAL**

**AUDIO DELAY LINE**

**MODEL BD955**

#### FULL BANDWIDTH PERFORMANCE

A multi-LED level indicator promotes proper level setting for maximum dynamic range. The standard unit provides full 15 kHz frequency response. For applications where wide band frequency response is not needed, such as the delaying only of 'phone signals, the user may opt for a 7.5 kHz model, at substantial cost saving.

# **MODEL BD955 BROADCAST DIGITAL DELAY LINE** specifications:

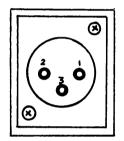

| INPUT CHARACTERISTICS  | Impedance nominal 10 k, balanced, maximum<br>level + 24 dBm. Full dynamic range from<br>0 to + 22 dBm levels. XLR female connectors.                    |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTPUT CHARACTERISTICS | Electronically balanced, maximum level + 22 dBm into 600 ohms. XLR male connector.                                                                      |

| DISTORTION             | Less than .3% at 1 kHz, reference level.                                                                                                                |

| DYNAMIC RANGE          | Greater than 90 dB from clipping to noise floor.                                                                                                        |

| DELAY                  | Memory capacity 3.2 or 6.4 seconds. Front panel<br>switch allows delay setting from about<br>6 ms to maximum.                                           |

| FREQUENCY RESPONSE     | 15 kHz $\pm$ 1 dB or 7.5 kHz $\pm$ 1 dB                                                                                                                 |

| SIZE                   | Requires 8.89 cm (3½ ") x 48.26 cm (19") panel space. Extends 31.75 cm (12½ ") behind panel.                                                            |

| POWER REQUIREMENTS     | 115 VAC, 50-60 Hz, or 230 VAC, 50-60 Hz.<br>Nominal power dissipation 40 watts.                                                                         |

| REMOTE CONTROL         | Control of the DUMP switch and indication of delay margin provided on the rear panel connector. Relay contact closure indicates manual DUMP activation. |

**NOTES:**

\* The pricing of the BD955 Broadcast Digital Delay Line is largely dependent upon the product of frequency response and delay. The customer is urged to consider his requirement carefully.

- \*

- For other frequency response or delay, request quotation. Once a unit has been purchased, it is possible to alter the maximum delay time with little trouble. IT IS IMPRACTICAL TO CHANGE THE FREQUENCY RESPONSE. \*

- STEREO CONNECTION for two units is available at a small extra charge. This allows either unit to be \* used as mono backup.

١

BD955 page 5.

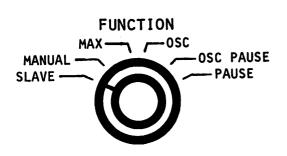

The FUNCTION control determines the mode of operation of the BD955 delay unit. Its six rotary positions operate as follows:

SLAVE: Configures the delay line to receive delay change commands from another BD955. l n this mode, the cable provided with a master/slave combination must be connected to both Both DUMP switches are connected in units. parallel, and activating either is equivalent to pressing both simultaneously. After the delay is reset by the DUMP button, the delay of both units will increase synchronously. IMPOR-TANT NOTE: SLAVE operation does not transfer the MANUAL control setting from one unit to the other. If it is desired to operate the master unit in the MANUAL mode, the SLAVE must also be in MANUAL, and both MANUAL DELAY controls should be set identically.

MANUAL: In this mode, the MANUAL DELAY control determines the delay setting of the unit. Refer to the MANUAL DELAY control description for information on settings.

MAXimum: Setting the FUNCTION switch to this position assures that the catchup rate will be as fast as permitted by the internal timing. This position is equivalent to the rate obtained by setting the unit to OSC with the catchup rate at maximum, or to PAUSE operation with no input signal.

OSCillator: In this position, the catchup rate is determined by an internal oscillator. The speed of the oscillator is determined by the CATCHUP RATE control. Because signal characteristics are not taken into account, operation of the oscillator will be more obtrusive than use of the PAUSE mode.

OSC PAUSE: This mode is a combination of the oscillator and pause modes. It is used primarily to assure that catchup will occur even with continuous program material. In operation, catchup will occur at the oscillator rate if no pauses occur, or faster (and less obtrusively) if they do.

PAUSE: This mode causes the delay to increment whenever the input signal drops below a certain threshold. Thus, delay is increased during syllabic pauses in speech or silent periods in programming. Because these pauses occur during low signal intervals, this mode is the least obtrusive.

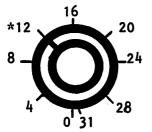

#### MANUAL DELAY CONTROL

When the FUNCTION switch is in the MANUAL position, the delay is determined by the MANUAL DE-LAY control. This is a 32 position rotary switch with no stop, so that it may be continuously rotated. No calibrations are included on the front panel because the delay is not only a function of the switch setting, but also of the options (delay/frequency response) purchased. The table below shows the approximate delay obtained at each switch setting.

#### Note three special positions:

Position 0 is always zero delay.

Position 31 is always maximum delay.

Postion 12 is the closest approximation to the round-trip delay time by a video signal transmitted to a geosynchronous satellite. This permits an audio signal transmitted by landline to be delayed conveniently so that audio and video may be synchronized.

| SWITCH                                                                                                                                                                                  | 15KHZ U |        | DELAY TIM                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | KHZ UNITS                                                                                                                                                                                                                                                                                                                                                                         | 1 6650                                                                                                                                                                                                                                 | MAX DELAY                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|                                                                                                                                                                                         | 0.45EU  | 3.25EL | 1.0SEC                                                                                                                                                                                                                                                                                                                                                                               | 0.45EU                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.2526                                                                                                                                                                                                                                                                                                                                                                            | 1.05EC                                                                                                                                                                                                                                 | MAX. DELAT                            |

| SETTING<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30 |         |        | 0         6.25         12.5         18.25         25         56         87         118         150         181         212         244         275         306         337         369         375         431         487         545         575         .631         .687         .768         .825         .906         1.01         1.12         1.20         1.33         1.46 | 7.5           0           12.5           25           37.5           50           62           125           137           150           162           175           237           250           262           375           437           450           562           675           837           950           1.16           1.37           1.64           1.90           2.26           2.73           3.23           3.80           4.51           5.37 | 0         12.5         25         37.5         50         62         125         137         150         162         175         237         250         262         325         387         400         462         575         637         700         .81         .975         1.08         1.20         1.41         1.63         1.89         2.10         2.41         2.77 | 1.6SEC<br>0<br>12.5<br>25<br>37.5<br>50<br>62<br>125<br>137<br>150<br>162<br>175<br>237<br>250<br>262<br>325<br>337<br>300<br>412<br>425<br>487<br>500<br>.562<br>.675<br>.737<br>.750<br>.862<br>.975<br>1.09<br>1.15<br>1.26<br>1.43 | MAX. DELAY<br>milliseconds<br>seconds |

DUMP CONTROL: This momentary push button switch initiates the deletion of program material in the following manner:

1: When the DUMP switch is depressed, the delay instantly goes to zero. It will remain at zero as long as the button is neld in. An internal relay closes when the switch is pressed, and opens about 1/2 second after the switch is released.

2: When the DUMP switch is released, the delay will increase according to the setting of the FUNCTION control.

3: Depressing the DUMP switch again before the delay has reached maximum will cause the delay to go to zero.

There is a potential conflict between the MAN-UAL DELAY control and the DUMP switch: When DUMP is depressed, the delay will go to zero regardless of the MANUAL DELAY setting. However, when the DUMP switch is released, the delay will immediately assume the MANUAL setting, if the FUNCTION switch is in the MANUAL position.

INPUT LEVEL: This control is a continuously variable attenuator which allows setting the unit to optimum operating level. The section on INPUT LEVEL SETTING gives criteria for proper adjustment of this control.

CATCHUP RATE: This control determines the rate of delay increase in the OSCillator mode, and the minimum rate of delay increase in the OSC PAUSE mode. When fully counterclockwise, the catchup rate is maximum. When the control is fully clockwise, the rate is quite slow, and several minutes are required to achieve full delay.

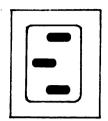

POWER ON/OFF: Placing this switch in the ON position applies AC power to the delay line. When power is applied and the unit is not in the MANUAL DELAY control mode, the delay is initialized to zero to prevent transients caused by reading invalid data from memory.

LINE IN/OUT: Depressing this control applies audio to the delay line, and enables its output. When it is OUT, there is a DC path from the input to the output, and power need not be applied.

CATCHUP RATE

INPUT\_LEVEL

Ni

POWER

IN/OUT

#### FRONT PANEL INDICATORS

IN/OUT LAMP: This LED is associated with the IN/OUT switch. When this switch is in the IN position, the LED becomes illuminated, signifying that the delay unit is IN line.

DELAY WARNING indicator group: These two color LED's advise and warn the operator how much delay margin the delay unit has built up. When the DUMP button is depressed, all six indicators turn red and flash periodically. This signifies that the delay is at or near zero and it is unsafe to place the phone caller on the air. As the delay time increases, the flashing red indication stops and the indicators, starting at the left, turn green. The number of indicators which have turned green show graphically how much time there is to edit the incoming program. One advantage of this indicator is that it is much easier to interpret than a When one or two green lights digital readout. are on, the operator knows that he must be especially alert; when they're all on, there's plenty of time to react. This feature allows resumption of program sooner than would otherwise be the case.

DUMP SWITCH LAMP: The incandescent lamp in this switch may be used in conjunction with the DELAY WARNING indicators: An internal jumper selects the drive point for this lamp so that when a selected green LED comes on, so does the DUMP lamp. This feature can be used to relieve the operator of judgement. He can be told "reactivate the 'phone when the light comes back on". Alternatively, the voltage controlling the lamp can be used to control the internal relay so that this relay disables the telephone during the period involved, thus preventing any possibility of human error.

11

SIGNAL LEVEL INDICATOR GROUP: These LED's function as a "bar graph" display which depicts peak audio input levels. The leftmost "PRE-SENT" indicator becomes illuminated when a small amount of signal is present. The PEAK indicator comes on when the digital system is on the verge of instantaneous clipping. The section on INPUT LEVEL SETTING describes this indicator and the associated INPUT LEVEL control.

-DELAY WARNING-000000

PRESENT

#### INPUT LEVEL SETTING

$\lfloor \rfloor$

1

1

The BD955 Digital Delay Line is similar to amplifiers, equalizers, tape recorders, transmitters, and virtually every other electronic device with the possible exception of a piece of wire at absolute zero in that it has a certain, limited, dynamic range. Dynamic range is defined as the levels between which operation of the device in question is useful or acceptable. As a practical matter, the range is usually bounded on the high side by excessive distortion, and the low side by excessive noise. In many equipments, a level indicating device such as the familiar VU meter is provided to indicate when the unit is operating at the proper level. A tape recorder, for instance, has a certain percentage of distortion at OVU, and this percentage rapidly increases as the signal level increases. The noise level is some number of decibels below OVU. The number of decibels between distortion and noise is defined as "dynamic range".

Signal sources typically have a dynamic range much greater than that of electronic devices. Likewise, the ear can hear a dynamic range much greater than that of electronic devices. Since the electronic device is the limiting factor, it is obviously a good idea to set the operating level of the delay line to take advantage of the maximum dynamic range of which it is capable. This is the equivalent of making sure that the meter on a tape recorder is reading around OVU most of the time.

To enable accurate setting of input level, a row of solid state indicators form a "bar graph" display underneath the INPUT LEVEL control. The lamps are graduated in level so that, with any significant input signal, the leftmost becomes illuminated, and, when the entire group is on, a clipping condition exists. With the INPUT LEVEL control fully clockwise, clipping will occur at about +6 dbm at 1 KHz. This typically corresponds to approximately OVU in most facilities. Of course some margin above OVU is required and consequently the INPUT LEVEL control will normally be operated between 12 and 3 o'clock.

The "ballistics" of the level display are such that it responds to instantaneous peaks. This fact, coupled with internal circuitry designed to reduce internal system gain as input level increases ("companding"), makes it desirable to operate the unit with the rightmost indicator flashing periodically. Such instantaneous peaks will generally be inaudible. The exception to this rule is when the delay line is connected in the audio chain following compression and limiting: in this case, the INPUT LEVEL should be set so that the second rightmost lamp is flashing frequently, and the rightmost virtually never.

As the dynamic range of the delay line is about 90db, following this procedure will insure that it is not the factor limiting performance of even the widest dynamic range stations.

FROM FUNCTION SWITCH (WIPER)

EXTERNAL SWITCH CLOSURE TO GROUND ACTI-VATES DUMP. (pins 1,7.)

Pins 4 and 6 are spare and may be used for modifications.

REAR PANEL CONNECTORS

AC POWER CONNECTOR: This connector accepts an internationally approved "IEC" connector. The line cord furnished with the unit is for United States standard 3 wire outlets. The line voltage is specified on the serial number plate, and may be changed from 115VAC to 230VAC by a simple internal wiring change.

FUSE HOLDER: The fuse in this holder is in the primary circuit of the power transformer. It should be replaced only with a 1/2 amp slo blo (115VAC) or a 1/4 amp slo blo (230VAC).

OUTPUT CONNECTOR (3PIN XLR MALE): This is the audio output connector for the delay line. Refer to the specifications for levels and impedances.

PIN 1 is shield/chassis ground.

Pin 2 is output -phase.

Pin 3 is output +phase.

INPUT CONNECTOR (3PIN XLR FEMALE): This is the audio input connector for the delay line. Refer to the specifications for levels and impedances.

Pin 1 is shield/chassis ground.

- Pin 2 is input -phase.

- Pin 3 is input +phase.

NOTE: For both input and output, the signal phase is arbitrary except at the very shortest delays, as many wavelengths of any given signal will be in the delay at any time. For phase checking, therefore, the delay should be set at 0.

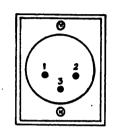

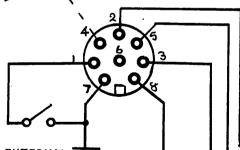

REMOTE CONNECTOR (8 PIN DIN FEMALE): This connector provides input and output connections for remote control of the DUMP switch and external connection to the relay. See schematic below for connection.

> NORMALLY CLOSED: pins 2 and 3 NORMALLY OPEN: pins 3 and 5

INTERNAL RELAY CLOSES WHEN DUMP SWITCH DEPRESSED

Remote Connector (as seen from behind the unit).

IMPORTANT NOTE: This drawing is a REAR PHYSICAL VIEW of the plug. The numbers molded on the plug should be ignored as they are both illogical and do not correspond when supplied by different vendors.

When wiring the plug, connect your circuitry to the pins corresponding to the physical position shown on this drawing.

2 XY 1 ~  $\widehat{}$ ÷.

#### SYSTEM INTERCONNECTION

11

نے

11

-

Ľ

11

F

14

The BD955 may be used in a straight delay mode, or one may take advantage of the catch up mode. If it is being employed to replace an existing tape delay, it may be connected in the system identically to the tape unit, i.e., substitute the delay input and output connectors for the tape system input and output connectors. In this mode, the delay should be set to maximum and the DUMP switch never touched. Whatever control system currently exists may then be used without modification.

If this is a new installation, and you wish to have the versatility of the catch up mode and the use of fixed delay as well, there are several connection schemes and control methods that may be used, and other commercial or easily produced devices which will permit both.

$\left| \right|$ ---

....

#### THEORY OF OPERATION

÷.

i

ل**ہ** ز

11

1\_

| |

{ !

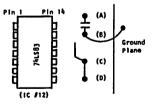

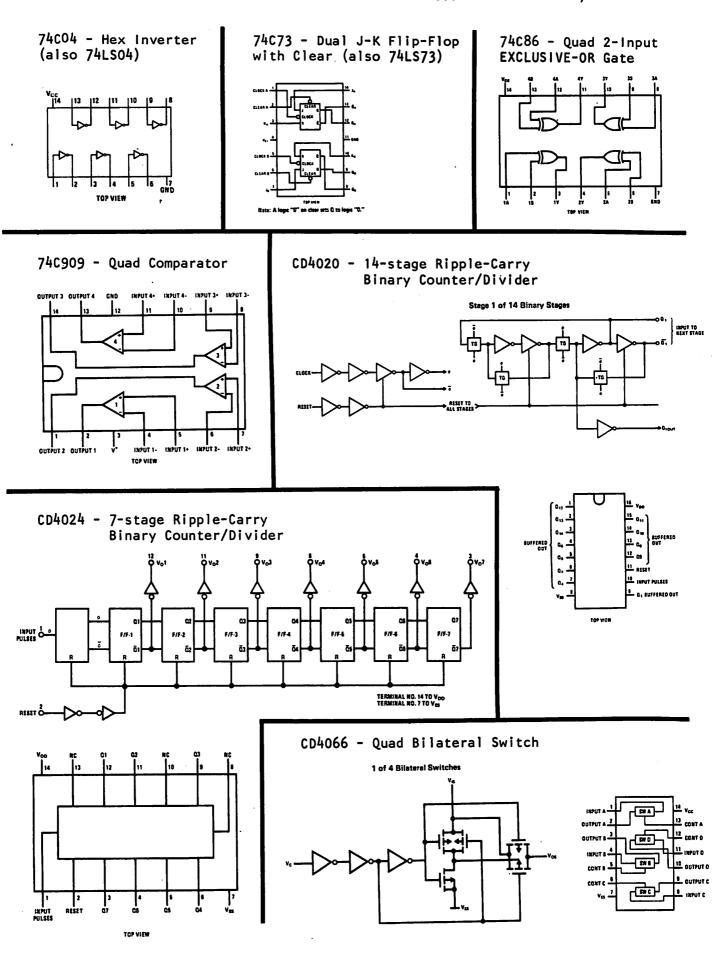

The purpose of this section is to describe in a fairly specific manner the method by which the delay line operates. The various circuit sub-groups are dealt with individually, with reference to what each one does and how it does it. To make this section of a manageable length, we assume that the reader is familiar with the individual integrated circuit "building blocks", and so will describe the IC's place in the scheme of things rather than the operation of the IC itself. Pin connections and brief descriptions of the IC's will be found at the end of this manual.

The circuitry of the BD955 Digital Delay Line is contained on three printed circuit assemblies. They are:

B955 Rev.- Main circuit and mother board

B951 Rev.- Random Access Memory board (B951 boards not used in units with s/n 95758 & above)

303C Rev.- Compressor/Expander boards (See page 24)

The only electronic components not on these boards are the +15 volt DC regulator (mounted on the right side of the chassis), the +5 volt DC regulator, (mounted on the rear of the chassis), and the power transformer. The various input, output, power, and control connectors are also located on the chassis. Six schematic drawings reference these assemblies, and should be referred to as an integral part of this section.

The power supply (schematic sheet #5) generates the regulated DC voltages required by the remainder of the circuitry. Full-wave bridge rectifiers generate raw DC at about +10V for the 5 volt supply, and at +/- 20 volts for the +15 regulated and -15 regulated supplies. The raw DC is regulated by IC regulators, mounted on the chassis in the case of the +5 and +15 supplies, and on the circuit board in the case of the -15 supply. Three silicon diodes in series with the +15 supply provide the 12 volts required by the memory array, and a zener diode/pnp transistor regulator provides the -5V (at very low current) required as bias for the memories. The 5V is employed by the digital logic as a power supply and, after filtering, as a bias supply for the analog circuitry. The + and - 15 volt supplies are used by the analog circuitry and output amplifiers.

#### TIMING OSCILLATOR:

IC33, sheet #2, a high-speed emitter-coupled oscillator provides basic timing for the system. All clocks are derived from this signal by various dividers and counters. This oscillator operates in the 100MHz range and there exists a possibility for interference if the delay line is mounted in close proximity to an FM tuner. If this should occur, it is permissible to retune the oscillator slightly without adverse effects on the rest of the unit. The output of the oscillator is applied to IC-34, a low power divide by 16 circuit, and to the input of the first counter in the analog to digital (A/D) converter.

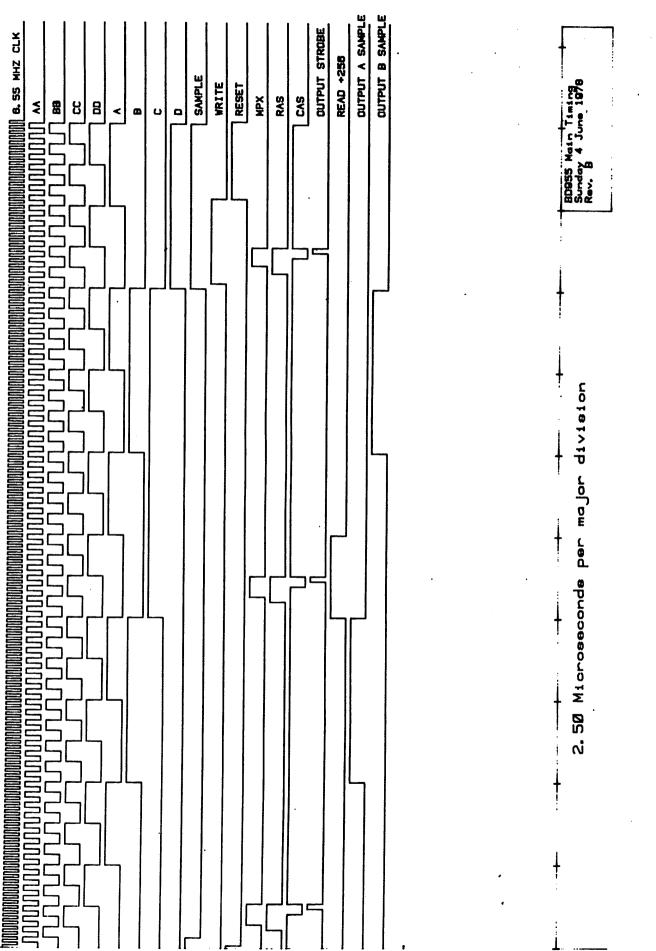

TIMING CHAIN: The output of the divide by 16 counter is connected to the synchronous timing generator consisting of IC's 47 through 52, and IC 54 (sheet #1). IC's 47 and 50 divide the 6MHz output of IC34 by an additional factor of 16 (IC 47) times 10 (IC50). The outputs of the these two IC's are decoded into unique time slots by read-only-memories (ROM's) IC-48 and IC-51, so that events can be initiated at the proper times. The ROM's are asynchronous, and latches IC-49 and IC-52 are used to "deglitch" the ROM outputs and apply the signals to the rest of the system. IC-54 is a flip-flop synchronously set and reset whose period is a few 100MHz cycles shorter than the maximum count of the A/D converter, and whose output enables the A/D counter. This circuit effectively prevents overflow of the A/D. The inter-relation of the timing signals produced by this circuitry is shown in the timing diagram.

#### ANALOG/DIGITAL CONVERTER

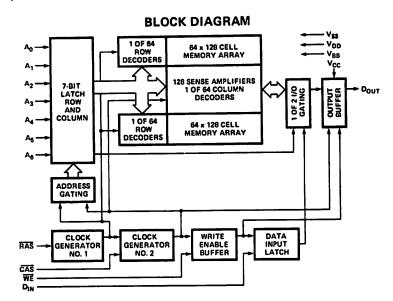

The Analog to Digital converter changes the analog input signal into the discrete voltage levels required for storage in the digital memory. This is accomplished by "sampling" the input signal at a fixed interval (determined by the timing circuitry described above) and measuring the voltage of the sample. The process is as follows: (refer to schematic sheet 2) The input signal is applied to IC-43 pin 8 at all times. IC-43 is a quad 1: CMOS analog switch. During the "sample" interval, the .0039uF capacitor is charged to the voltage of the input. When the sample pulse is turned off, the capacitor is linearly discharged by a current sink. The discharge time is a linear function of the initial voltage. Comparator IC-44 detects when the voltage on the capacitor reaches 0 volts. IC-29 is a gate which enables counter IC-32 during the period between the end of the sample pulse and the time when the capacitor voltage reaches zero. This time is proportional to the instantaneous voltage present on the capacitor at the end of the sample pulse, and is measured by the counter chain IC-30, 31, and 32. Each successive stage of the counter divides the previous input by two. The maximum count period, determined by IC-54, is just nanoseconds less than that required for the counter to reach a count of 2048, or 2 to the 11th power. Thus the A/D converter is capable of resolving "11 bits", which corresponds to an instantaneous dynamic range of about 66db. The outputs from the counter form the data word written into the memory under control of the timing circuitry.

The front panel level indicator is operated directly from the A/D converter: A 4 bit comparator, IC-28, compares the current value of the input signal with the state of the 4 bit counter IC-27. If the input signal is greater, then this new, larger value is strobed into the counter. If it is lower, the counter remains as-is. Thus, these two IC's form an instantaneous peak detector. The signal labelled "FLASH" is a slow speed clock which asynchronously decrements IC-27. This signal is orders of magnitude slower than the peak detection function. If no peak comes along, however, the counter slowly counts down. IC-26 is a ROM programmed to turn on various front panel LED's in response to the state of the decrementing counter. An additional output from the ROM inhibits the counter from going below zero and "wrapping around", thus causing repeated cycling of the level indicator.

#### INPUT SIGNAL CONDITIONING

Before reaching the A/D converter, the input signal must be conditioned. The conditioning includes compression which, with complementary expansion on the greatly increases the DDL dynamic range, and filtering, which deoutput. creases the amplitude of high frequency signals which could cause spurious responses from the DDL, known as "aliasing". The signal must also be offset to +5VDC, so that the converter, which is inherently unipolar, can convert AC IC-46 comprises four operational amplifiers. The first section is signals. a differential amplifier which provides a balanced input and large input vol-Following the LEVEL control comes a gain stage and two three tage range. pole low-pass filters to perform the anti-aliasing function. The compressor card has two sections, a voltage-controlled-amplifier (VCA), and a level Unlike the normal compressor, these sections operate independetector. dently.

BD955 page 15.

The input level is measured and fed to the VCA in such a manner that, for each 6db increase in input level, the gain of the VCA is decreased by 3dB. This provides a 2:1 compression ratio over a very wide dynamic range. The two .1uF capacitors and the resistors associated with this assembly are a high-pass filter to remove sub-audible frequencies (such as turntable rumble) from the input. The network between the compressor output and 1C-45 allows biasing of the signal to +5volts as required by the A/D.

1 1

Ignoring the intervening delay circuitry temporarily, the output circuitry comprises a D/A converter and the associated circuitry required to change the digital numbers removed from the memory back to an audio signal. There are additional complications involved in this process, so we will discuss the normal mode first, and then show what happens during the "catch-up" mode.

IC's 35 and 36 are 6 bit latches which are strobed when each word becomes available at the memory output. This datum is applied to the input of D/A converter IC-37. This converter is a special type called a "4-quadrant multiplying" D/A. This means that the output current or voltage (in this case, current) is the product of the digital word and a reference voltage applied to the reference input pin 17. Assume temporarily that the reference is fixed at -10 volts. As each word is input, it is converted from a current output to an offset bipolar voltage by IC-41. The circuit constants are such that with a half scale digital input, the output voltage is 5 volts. As the input varies between zero and full scale, the output varies between 0 and +10V. (If the reference voltage is decreased, the offset remains the same but the full-scale amplitude decreases so that with a reference of 0, the output remains at 5 volts.)

After the voltage is available at the output of IC-41, it is sampled by another analog switch identical to the one used in the input sam-IC-43. The output of this switch is amplified by IC-42 (pins 5,6,7) and pler. then filtered as done in the input by a section of IC-45. This filtered signal is expanded in a fashion complementary to the compression performed I.e., the gain of the VCA is increased by 6db for each 6db at the input. increase in the signal level. This "companding" operation reduces by a factor of 2 the range of the signal going through the digital system and Noise pickup and would theoretically give a dynamic range of over 120db. other effects necessarily limit the improvement, but it is nonetheless quite dramatic. The output of the expander is applied to two sections of IC-45 which, together with their transistor buffers, comprise the output These circuits are of identical gain but opposite phase, so a amplifiers. quasi "balanced" output is available without response-degrading transform-The peak to peak output level is also doubled. The output impedance ers. is 300 ohms (150 ohms single ended), and suitable for driving any type of The 10 ohm resistors in the collector circuit decouple the buffer load. from the power supply and act as fuses if the output is accidentally shorted during test. (Shorting the output after the 150 ohm resistors is not harmful and can be endured indefinitely.)

#### THE CATCH-UP MODE

A unique feature of the DDL is its ability slowly and almost inaudibly to insert delay in live program so that time may be "caught up" without insertion of artificial pauses or putting extraneous material on the air. The key to this capability is the ability of the random access memory to look at various locations (delay times) upon instantaneous command. Each time a catch-up command "JUMP" is issued, the output of the delay line is displaced 256 samples, roughly 8 milliseconds, farther from the input, thus increasing the delay by that amount. This must be done as unobtrusively as possible. If it were done the obvious way, by reading in data at one rate and reading it out at another, slower rate, it would result in a continuous pitch shift which would abruptly terminate when the maximum delay is reached. This is unacceptable, so the jump method operates as follows:

Assume you are looking at a signal at time A and that you want to listen at time B, 8 milliseconds later: You can't simply switch times, because there would be an audible splice. This is the digital equivalent of splicing a tape without an angled cut. The digital equivalent of the 45 degree angle is synthesized using the previously unmentioned circuitry of the D/A section.

The output of the memory is actually sampled twice for each input sample. One sample reads the current value of the signal (sample A), and another sample reads the value 256 samples later. Normally, the second sample (sample B) is ignored by forcing the reference voltage on the D/A to be However, when the JUMP zero during the time the B data is in the latch. command is received, a counter, IC-40 is enabled. This counter, in conjunction with exclusive-OR gates IC's 38 and 39, forms a ramp generator which controls the reference voltage on the DAC. Normally, during sample A, the output is -10V, and 0 during sample B. As IC-40 increments, the A sample reference decreases to 0 and the B sample reference increases to Each step of the ramp occupies one sample period, so that the tran--10V. sition is not abrupt. Note that another section of switching IC 43 samples the B output. Both outputs are combined in IC-42 (pins 5,6,7).

The effect of all this is that, when a JUMP command is received, the amplitude of the current signal is decreased and the amplitude of the delayed signal is simultaneously increased. Because of the method of generation of the reference voltage, the sum of the two amplitudes is constant, thus providing a smooth transition (splice). At the end of the ramp interval, the counter is instantaneously reset, the A output incremented by 256 samples, and the B output disabled. Thus the next sample (at full amplitude) is equivalent to what would have been the next B sample. The B output is meanwhile ready for another increment.

#### CONTROLLING THE JUMP COMMAND

As smooth as the transition is, it is not inaudible. There will usually be some difference between the signals at the different times, and this will show up as a combination of phase and amplitude modulation of the output signal. This is sometimes unavoidable, but there is one further precaution one can take: If the JUMP takes place during a period of no signal, then there will be no splice "glitch". The major anticipated use for this unit is for changing delay during talk programming. Speech is characterized by many pauses, both syllabic and deliberate, for thinking, effect, or whatever. By carefully tailoring circuit time constants to these pauses, it is possible to add delay during natural pauses in speech. Splices so occuring are inaudible. The subjective effect, during catch-up, is that the speaker is talking a bit more slowly, but there is no pitch change and no distortion introduced! Additional catch-up modes are provided: If music programming, in which pauses are much less frequent, is contemplated, a variable rate oscillator can be used to initiate the JUMP command.

Because the pauses occur asynchronously with system timing, a bit of extra Refer to sheet 1: When a JUMP command is received logic is required. Assuming that a JUMP has not oc-(NJREQ), a S-R flip-flop (IC-55) is set. curred too recently, this request is passed through IC-53 (1,2,3) to IC-55 (8,9,10) which further qualifies the request by determining whether maximum delay has yet been reached, signified by a logic low at the FULL gate output. If it has not, IC-61 is set. This flip-flop enables the B output strobe. When a JUMP begins, the enable flip-flop, IC-54 is reset. This prevents another jump from occurring too soon. If this were not done, the jumps could be continuous and the output would be cut down to zero (catch-up rate same as The maximum rate is thus determined by the input pulses real time passage). Transition of the most significant bit on the ramp generator to IC-59。 signifies the end of the jump, which permits the process to begin at the first jump request after the enable flop has been toggled.

The request rate is determined by the function switch. If the NJREQ line is grounded (MAX position), then jumps occur as fast as they are enabled. A relaxation oscillator (IC-60) can vary the rate substantially. In the OSC mode, the capacitor on the input of IC-60 is slowly charged through the front panel CATCHUP RATE control. When the capacitor reaches the threshold voltage determined by the resistor network connected to pin 3, pin 6 goes low, issuing the request. The digital circuitry then discharges the capacitor so that after the jump it must re-charge before a new request can occur.

1C-56 amplifies the A output The jump on PAUSE circuit works as follows: only. Its gain is controlled by a circuit board mounted trimpot, R1. (This adjustment can be changed to accommodate different talkers. IC's 57 and 58 form a dual threshold comparator. If the output from IC-56 crosses either threshold, the capacitor on the input to IC-59 is discharged through one of the diodes pointing to the comparator input. If there is a pause in the input signal, neither threshold is crossed, and the capacitor slowly charges through the resistor connected to +15V. When the capacitor voltage reaches the threshold of IC 59, again determined by the resistor network, a jump request is issued. In this case, the capacitor is not discharged by the digital circuitry, as we wish to take advantage of the pause as long as The final mode, "BOTH", is a logical OR (a NAND gate is performpossible. ing the OR function) of the PAUSE and OSC modes. In this case, if a pause occurs, the oscillator remains inactive, but if it doesn't, catch up is forced by the oscillator.

When JUMP REQUEST (JREQ) goes LOW, a jump is initiated on the next JUMP ENABLE. If JUMP REQUEST remains low past the end of JUMP-IN-PROGRESS (JIP), an additional jump is initiated at the next JUMP ENABLE positive transition.

During a JUMP, the signal envelope is the sum of the signal multiplied by the channel A gain, and the signal delayed by 256 samples multiplied by the channel B gain. Because the signals may be in or out of phase (or in any phase relationship, for that matter), the signal envelope may have two partial nulls or one full null during the JUMP. If the signal is not a sine wave or other repetitive signal, this effect will be hard to observe, but audible nonetheless unless the PAUSE mode is in use.

Sheet 3 of the schematic diagrams contains the circuitry which actually controls the delay. The various counters and adders on this sheet determine the read and write addresses of the RAM, which contains data corresponding to the input data stream in consecutive order. The process works as follows:

#### WRITING DATA TO THE MEMORY

l

IC's 7 through 10 form a binary counter chain which is decremented every time a new word is written into RAM. The five chips have a count capacity of 2 to the 20th power, or about 1 million counts. The maximum capacity of the delay line is 1/4 of this, so the top two bits are ignored. Depending upon the card complement installed, fewer bits may be used. Each bit combination corresponds to one and only one address in the RAM array. The array uses 16K bit integrated circuits which have 2 to the 14th power storage locations. All chips get the bottom 14 bits applied to their address inputs. The next bit selects the individual row on the memory card, and the remaining (up to 3) bits uniquely select the card.

Once the A/D converter has completed a conversion, the data is placed on the memory DATA input lines (as opposed to ADDRESS lines, determined by the counter, above). This data is written into the addressed location, and the counter is decremented. On the next write command, a data word is written into the next (lower) memory location. This continues until the entire memory is filled, at which point the first location is overwritten with new data. The procedure can be likened to recording on a tape loop: When a point comes around again, whatever is present is erased and a new signal is impressed on the tape.

This write operation is performed at the sampling rate of the DDL. Thus, each address corresponds to an input sample. Since the counter, referred to as the "BASE ADDRESS REGISTER" is decrementing, it can be seen that looking at an address positively offset from the base address by a certain number of samples will show the same sample which was input that number of sample periods earlier. Thus, reading data from the memory +1000 samples from the register corresponds to a delay of 1000 sample periods (about 30 milliseconds).

The adders (IC's 11 through 13) accomplish this during READ operations. Note that one set of inputs to the adders is from the base address register. The other is from a group of AND gates whose inputs in turn are enabled by NWRITE. This means that the second input to the adders will always be 0 during write operations, forcing the write address to be equal to the base address. We shall refer to the read operations as READ A and READ B, depending upon the time slot during which they occur (and, of course the use made of the data). During normal operation (no jump request), READ A is performed as follows: The counter chain IC's 20 through 22 contains the fixed delay data. This is passed through the group of adders formed by IC's 17 through 19. Since all other inputs are grounded at this time, the adder output is identical to the adder input. This group of adders feeds its output through the AND gates to the first group of adders. Because the AND gates are now enabthe read address equals the sum of the base address and the delay setled. ting counter.

Thus the READ A operation retrieves data from the memory at the current delay setting the the DDL.

The READ B operation is identical, except that the +256 input of the adders feeding the AND gates is now enabled. The output of these adders is therefore the input (the current delay register) + 256, giving the B delay required when summed with the base address register. These are the only memory reference operations which occur in the DDL. Although dynamic memories are used, there is effectively no refresh requirement because all accesses are unconditional and sequential, thus guaranteeing that all row addresses are read in the required length of time.

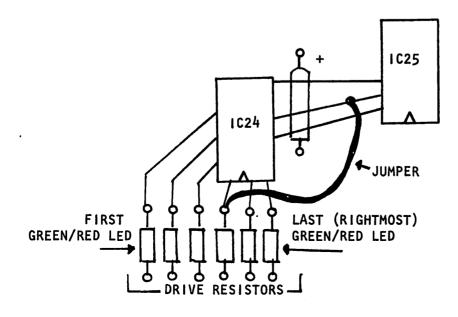

One additional mode of operation is controlled by the memory logic circuitry: The delay register/counter group may be manually set, in addition to being incremented after each jump request. The NMANUAL line activates the PRESET inputs of the counters allowing front panel control of the delay. IC-24 is a ROM which controls the operation of the front panel LED's which indicate the These are RED/GREEN leds, and the polarity of the ROM output current delay. is such that when little or no delay is set, the lights all come on RED, while as delay increases, the lamps turn green sequentially. As an additional warning, the FLASH signal enables the ROM when the lights are red so that they flash on and off. The FLASH signal is derived from the base address register. The NFULL signal is provided to stop the delay counter from incrementing when the memory capacity of the unit is reached. NFULL is decoded by selecting the inputs to IC-23 with a PC board mounted DIP switch. To indicate FULL, all inputs must be 1's. If the corresponding switch is open, the input will automatically be 1. If the switch is closed, the gate waits until that bit in the counter is true.

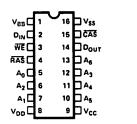

The memory array decoding is performed by IC's 1, 2, and 6 (schematic sheet 1 and 2 are address multiplexers and operate under the control of the #4). Because 14 addresses are required for each memory IC, and size timing ROM。 limitations preclude the use of 14 address pins on the package, the addresses are multiplexed. During the first portion of the memory cycle (RAS, or Row Address Strobe), the multiplexers permit AO through A6, the least significant bits of the address, to be strobed onto the memory chip. The multiplexers are then switched to pass the next 7 bits (A7 through A13) to the IC. These are entered during CAS, or Column Address Strobe. The R/W (read/write) line is applied to all chips and determines whether the input data is to be stored, or whether output data is to be read. If a read operation is called data become available immediately (about 150 nanoseconds) after CAS. for, IC-6 decodes the board address implied by the output of the base address register and adder, and permits CAS to go to only the board which corresponds to the desired address. CAS strobes write data into the RAM, and enable the For this reason, each RAM's input and output may be connecoutput buffers. ted to the same line with no interaction.

The memory boards themselves contain two rows of memories and two TTL buffer chips. Thus all address and timing inputs present the system with a single load instead of the usual highly capacitive memory lines.

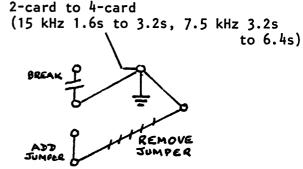

PLEASE NOTE: In units with s/n B95758 & <u>Above</u>, 8 cards is the equivalent of all four rows of 64K RAMs. 4 cards is equivalent to the top 2 rows of 64K RAMs. 2 Cards does not apply to newer units.

The one front panel control not discussed thus far is the "DUMP" switch (panic button). Refer to schematic sheet #1. This switch initiates the procedure whereby the data in the memory is effectively removed from the on-air program stream. It works as follows: Assume that the unit is operating at maximum delay, and one desires to delete the program material in the Pressing the DUMP switch instantly zeroes the delay register. The memory. DDL is brought back into real time, and data presently stored in memory is overwritten before the delay can catch up to it again. Simultaneously, a relay is closed for a variable period (depending upon purchase specifications). The relay is driven by a section of IC-62, a CMOS inverter with a The input capacitor (pin 5) is rapidly disvery high input impedance. charged, and the transistor driver turned on. When the capacitor charges to the gate threshold, the relay is turned off. The lamp in the DUMP button (driven by another section of IC-62 and a transistor) may be used to indicate when a certain amount of delay has been recovered. The switch is interfaced so that a similar switch may be connected in parallel, contact for contact, to provide a remote control. The relay contacts are also brought to a connector, and may be used to short out audio from the offending source, or for any other control function. Depending upon purchase specifications, other interface options may be provided.

Ĵ

BD955 page 22.

#### STEREO INTERCONNECTION

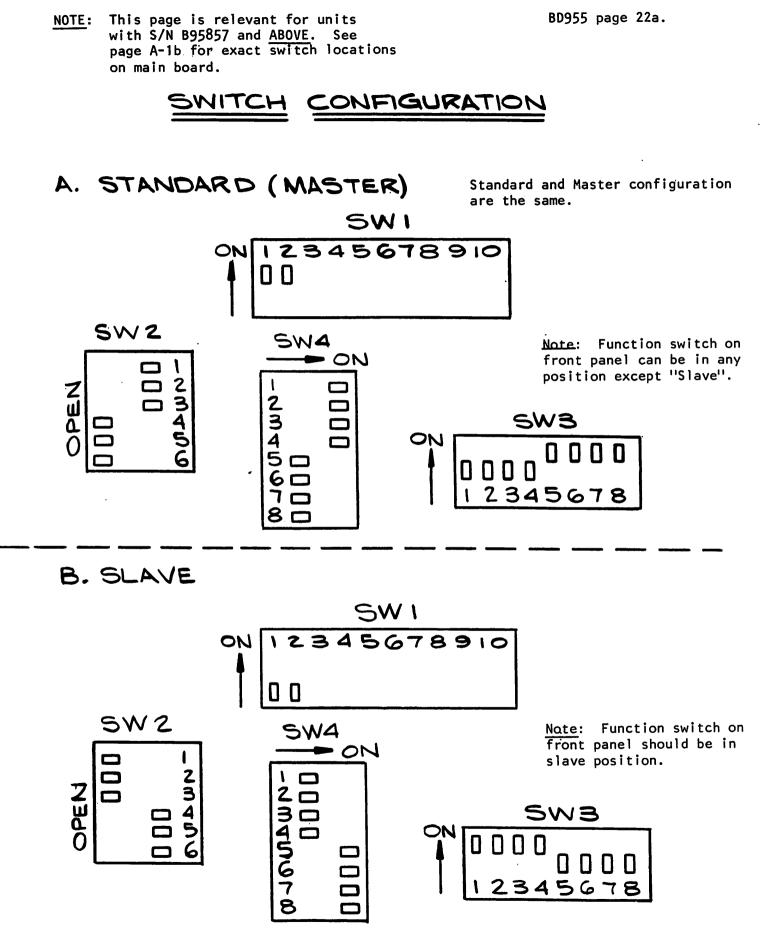

If so ordered, the BD955 may be provided with stereo interconnect facilities. When this is done, one unit acts as a master, and the other as a slave. The oscillator from the master provides the clock for the slave, and two logic signals, NJREQ, and NDUMP are cross connected to assure that the delays of both units remain identical. When two units are so connected, the operational characteristics of the second, "slave" unit differ from those encountered under normal operation.

When Master/Slave operation is desired, both units must be modified. This modification is relatively minor, and is normally provided by Eventide at the time of purchase. As mentioned in the Theory of Operation section, signals passed between the units are the master oscillator output, the jump request (which advances the delay) and the DUMP switch output. Electronic considerations require certain limitations on the slave unit to enable it to operate in this mode.

If a unit is designated as a slave, IT MUST BE CONNECTED TO ITS MASTER with the interconnecting cable provided to operate! This cable is quite short due to the high frequencies involved, and the units therefore must be mounted in the same rack, no more than about 7 inches apart. (The slave may be enabled to operate on its own in about 5 minutes, by undoing part of the modification. This requires opening the top cover and exchanging one socketed component for another.) For s/n B95857 & above, see page 22a for Master/Slave configuration.

When connected in the Master/Slave configuration, the following operating characteristics obtain.

1: The FUNCTION switch on the slave unit must be in the SLAVE position.

2: The INPUT LEVEL controls on both units remain independent.

3: All delay setting controls on the slave unit are ineffective.

4: The delay setting controls on the master unit affect only the master. 5: Pressing the DUMP switch on EITHER unit is equivalent to pressing the DUMP switch on BOTH units.

When the DUMP switch is pressed, both units will go to zero delay (unless the master is in a mode, such as MANUAL, in which the DUMP switch is ineffective), and then increase in delay according to the mode in which the master is set to operate. The slave will track the master in delay until delay reaches maximum, at which time, both units will stop at their final delay.

In the above discussion, it is assumed that both units are identical in terms of delay options. If the master and slave have different maximum delay capabilities, the unit with a greater delay will continue incrementing after the other stops. This is clearly undesirable because the whole purpose of stereo synchronization is to keep the channel delays equal. The way to avoid this problem is to set the dip switches at the input to the FULL gate identically in both units, and to a setting no greater than the maximum delay of the shortest unit.

If the DUMP and catchup capability is not being employed, it is permissable to set both FUNCTION switches to the manual mode and set the delays identically. If this is done, the DUMP switch may still be used to trip the internal relay and control whatever external circuitry it may be connected to. However, it will have no effect on the delay of either DDL. (Again, both DUMP switches are wired in parallel so that pressing either is equivalent to pressing both.)

11

ĥ

BD955 page 23.

#### INTERNAL ADJUSTMENTS AND ALIGNMENT PROCEDURE

Ľ

1

1 1

There are several internal adjustments in the BD955. These are adjusted at the factory, and should not need readjustment or alignment. Some of these adjustments may be used to alter the operating characteristics of the unit, and as a convenience to the user are detailed here. All the adjustments are again mentioned in the alignment procedure.

PAUSE LEVEL CONTROL: This is a single turn trimpot (R1) located on the main circuit board immediately to the left of the front leg of the right hand compander card (see parts location diagram). This control sets the threshold level of the PAUSE DETECTOR circuit, and is factory adjusted so that catch up will occur at a reasonable rate with normal speech. If desired, the threshold can be increased or decreased. Turning the control clockwise decreases the threshold, which means that a lower level signal will prevent a jump from occurring. This tends to slow down the catchup procedure, but makes it less audible. Turning the control counterclockwise increases the threshold, which speeds up the catchup rate, but makes the glitches more audible. The final setting is of course a compromise between long waiting and poor quality.

OSCILLATOR FREQUENCY: The master oscillator runs at about 104MHz to provide timing signals for the digital logic. Its frequency is controlled by an inductor on the far right side of the main circuit board and about half way back. (7.5KHz delay lines run at half this frequency.) Although the unit is well shielded, it is possible that enough spurious radiation may leak out to be picked up by an FM receiver located within a few feet. If your station happens to be on the same frequency as the master oscillator, and you are monitoring the air signal on an FM receiver a few feet from the DDL, and you pick up the master oscillator. We suggest the latter. Slight changes (up to a few hundred KHz) will not affect the rest of the circuitry and no readjustment or realignment will be required. A plastic hex alignment tool or even a hex (Allen) wrench may be used, the latter carefully.

INPUT GAIN: This control is located on the left hand compander card (second control from the left looking at the card from the front panel). The gain of the delay line is factory adjusted to give full output with a +6dBm input signal with the INPUT LEVEL control at maximum. If this unit is being used at unusually low levels (for instance, with such "semi professional" equipment as TASCAM consoles and the like), it may be desired to increase the gain. This may be done by rotating the control clockwise. There is no reason why the gain would have to be decreased, as the INPUT LEVEL control handles this chore. Although the internal gain control has a very wide range, it should not be used to make up gain for which a preamplifier should be used, as the noise performance of the DDL will suffer. Increasing the gain by up to 10dB should have no material effect on the dynamic range.

OUTPUT GAIN: This control is located on the right hand compander card (third control from left, looking at the front panel). This control may be used to decrease the output level when feeding inputs which cannot handle +22dBm signals. Again, the control has a wide range, but large changes should be effected by a resistive pad rather than by this control.

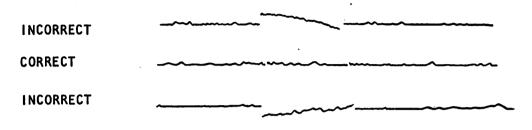

A/D CONVERTER WAVEFORMS

The BD955 will have either two DBX 303 boards (interchangeable) or two DBX cards that act specifically as either a compressor or expander.

#### ALIGNMENT

$\bigcup$

Equipment required for alignment consists of a low distortion sine wave oscillator, a distortion meter or spectrum analyzer, and an oscilloscope. The oscilloscope should either be a dual trace unit or have an external trigger input.

OSCILLATOR FREQUENCY ADJUSTMENT: Note that this is not a critical adjustment unless for some reason you need exactly 6.4 seconds of delay! Any reasonable tolerance is OK, although a frequency counter may be used for precision. Attach the scope probe to pin 7 of IC-50. You should observe a 5V pulse waveform with a 1/5 duty cycle. Adjust the oscillator coil for a repetition rate of 40.96kHz, or a pulse period of 24.41 microseconds.

ANALOG/DIGITAL CONVERTER CURRENT SINK ADJUSTMENT: The control for this adjustment (R2) is immediately behind the rightmost control on the right hand compander card. Trigger the oscilloscope on pin 7 of IC-50 (same pin as last step). Adjust the scope so that falling edge of the pulse is at the left edge of the screen and the rising edge is at the right edge of the screen. The full screen corresponds to the conversion period. Adjust the gain of the other scope channel to 1 volt per division and with no input, put the baseline 1 division above the bottom of the screen. Now put the scope probe on pin 5 of IC-44. (Note: use a good scope probe. A high capacitance cable can disturb this measurement.) Adjust the sink current control so that the sawtooth signal on the screen crosses the center horizontal division of the scope screen at ground level (1 vertical division up).

NOTE: For all analog adjustments following, set the DDL in manual for zero delay. The distortion meter should have its high frequency cut filter IN.

INPUT COMPANDER: This is the left compander plug-in circuit card. Apply a 1kHz, +6dbm signal to the input of the DDL. Turn the front panel INPUT LEVEL control fully clockwise. Adjust the gain control (second from the left) so that the PEAK front panel LED is just turning on. Attach the distortion meter probe to pin 8 of the output (right hand) compander card. Adjust the HF distortion control on the left of the compander for minimum distortion. Reduce the input frequency to 80Hz and adjust the LF distortion for minimum distortion. As this adjustment may have some affect on level, repeat the first two steps of this procedure as required.

OUTPUT COMPANDER. With the input signal at 1KHz, adjust the front panel IN-PUT LEVEL control so that the left four level indicating LED's are illuminated. Alternating between 1KHz and 80Hz, adjust the HF and LF distortion controls for minimum distortion as measured at the output connector of the DDL. When distortion has been minimized, increase the INPUT LEVEL control until the PEAK LED just comes on. Now, adjust the output gain control on the compander card (second from the right) until the signal measured between pin 1 and pin 3 of the output connector measures about 20V peak to peak or about 6.5V rms.

As a final check, increase the signal level at the DDL input by 2dB. The output should begin to show clipping at this level.

PAUSE LEVEL CONTROL: Place the DDL in the PAUSE mode and monitor IC-55 pin 1 with the scope. Reduce the input signal to 40dB below clipping and adjust the control (R1) until the signal is just changing state. This adjustment may be made for different signal levels as detailed earlier.

BD955 page 26.

A/B OFFSET CONTROL ADJUSTMENT (R3): This control is located to the left of IC-41 on the right rear of the circuit board. Its purpose is to equalize the DC levels of both output channels so that there is no DC shift when changing from the A output to the B output and back again. This control should be checked if any of the power supply regulators ever has to be replaced. Set the oscilloscope for a sweep rate of 5 milliseconds per division. Remove the input signal from the DDL and set the function control to the OSCillator position. Set the catchup rate fully counterclockwise. Attach the scope probe to pin 7 of IC-42. Depending upon the present setting of the control, you may observe a broken baseline with periodic level shifts. The fixed portion is about 30 milliseconds long, and the shifted portion is about 10 milliseconds. The relative polarities of these lines depend upon the control setting. The control should be adjusted to minimize the level shift. It is possible to adjust the control for zero shift, but it will drift slightly with age. Small shifts are generally below the noise level and may therefore be ignored, but if the control is seriously misadjusted, a "rumbling" quality can be imparted to the signal at high catchup rates.

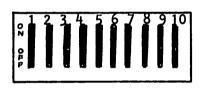

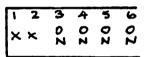

"FULL GATE" INPUT DIP SWITCH: This group of switches is adjusted at the factory, and together with the configuration ROM's, LC oscillator values, and filter components determines the configuration of the DDL in terms of frequency response and delay. This control should be set depending upon the number of delay cards installed in the unit (regardless of frequency response):

8 cards: 3,4,5, and 6 ON. (For units with s/n B95758 & Above, please 4 cards: 3,4, and 5 ON see note at the bottom of BD955 page 20.) 2 cards: 3 and 4 ON

The other switches have no function on the standard unit but may be used for custom modifications. If they are in use, this manual will contain an addendum covering their operation.

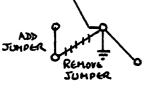

DUMP LAMP JUMPER: This is a short wire that is used to determine when, in relation to the total delay, the light in the DUMP switch becomes illuminated. By changing the jumper location, one may select different time intervals. See drawing below.

DUMP LAMP JUMPER LOCATION

A/B OFFSET POT ADJUSTMENT

DIPSWITCH

.

L

J

1

U

#### TROUBLESHOOTING, emergency and otherwise:

The BD955 is a reasonably complicated electronic device, employing several hundred semiconductor devices, including the "state of the art" 16K Random Access Memory. It has been designed to achieve high reliability by using low power components, a conservatively rated power supply, and taking care to avoid potential problems. None of the foregoing means that it can't break down, however, and this section is designed to help you get it going again.

Despite the plethora of IC's in the unit, it is possible to check it systematically. The potential problems can be broken into three major areas: The first is a system problem that prevents it from working at all. This could be a power supply or audio chain defect, or some problem in the timing chain. The second (and we think most likely) is a RAM failure. Finally, some problem in the JUMP circuitry could manifest itself. Of the three, only the first is really serious. A RAM problem, as will be seen, can almost inevitably be repaired in the field in a few minutes. A JUMP circuit problem can be gotten around temporarily by using maximum manual delay and troubleshot at leisure. Here are some abbreviated procedures:

TIMING CHAIN: Check pin 7 of IC-50. If pulses of the proper width and frequency are present, it means that the timing dividers are almost certainly working properly. If they aren't, work backwards to the master oscillator to find the defect.

POWER SUPPLY: Check for +5, +15, and -15 volts on the thick lines near the rear of the circuit board. Check for +12 and -5 volts on the memory plug in boards. If -5 is missing, you have a bad chip or shorted bypass capacitor: remove boards to isolate the problem.

AUDIO CHAIN: Ordinary signal tracing procedures will work here. Just follow the signal through the unit and change anything that seems to be stopping it.

COMPANDERS: The two compander cards are identical. If a problem is found with one, they can both be bypassed (with, of course S/N degradation) and the unit put back in service until the replacement arrives.